AM62A1-Q1

Overview

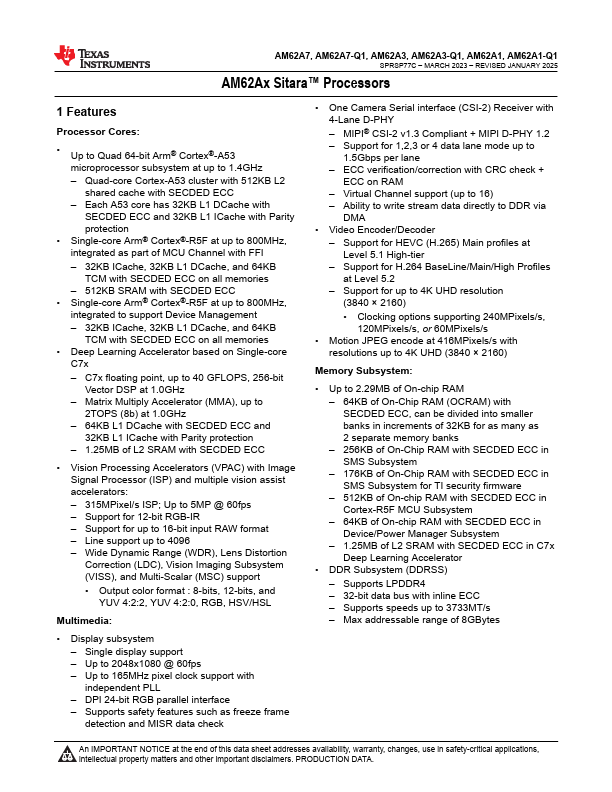

- Up to Quad 64-bit Arm® Cortex®-A53 microprocessor subsystem at up to 1.4GHz - Quad-core Cortex-A53 cluster with 512KB L2 shared cache with SECDED ECC - Each A53 core has 32KB L1 DCache with SECDED ECC and 32KB L1 ICache with Parity protection

- Single-core Arm® Cortex®-R5F at up to 800MHz, integrated as part of MCU Channel with FFI - 32KB ICache, 32KB L1 DCache, and 64KB TCM with SECDED ECC on all memories - 512KB SRAM with SECDED ECC

- Single-core Arm® Cortex®-R5F at up to 800MHz, integrated to support Device Management - 32KB ICache, 32KB L1 DCache, and 64KB TCM with SECDED ECC on all memories

- Deep Learning Accelerator based on Single-core C7x - C7x floating point, up to 40 GFLOPS, 256-bit Vector DSP at 1.0GHz - Matrix Multiply Accelerator (MMA), up to 2TOPS (8b) at 1.0GHz - 64KB L1 DCache with SECDED ECC and 32KB L1 ICache with Parity protection - 1.25MB of L2 SRAM with SECDED ECC

- Vision Processing Accelerators (VPAC) with Image Signal Processor (ISP) and multiple vision assist accelerators: - 315MPixel/s ISP; Up to 5MP @ 60fps - Support for 12-bit RGB-IR - Support for up to 16-bit input RAW format - Line support up to 4096 - Wide Dynamic Range (WDR), Lens Distortion Correction (LDC), Vision Imaging Subsystem (VISS), and Multi-Scalar (MSC) support

- Output color format : 8-bits, 12-bits, and YUV 4:2:2, YUV 4:2:0, RGB, HSV/HSL Multimedia:

- Display subsystem - Single display support - Up to 2048x1080 @ 60fps - Up to 165MHz pixel clock support with independent PLL - DPI 24-bit RGB parallel interface - Supports safety features such as freeze frame detection and MISR data check

- One Camera Serial interface (CSI-2) Receiver with 4-Lane D-PHY - MIPI® CSI-2 v1.3 Compliant + MIPI D-PHY 1.2 - Support for 1,2,3 or 4 data lane mode up to