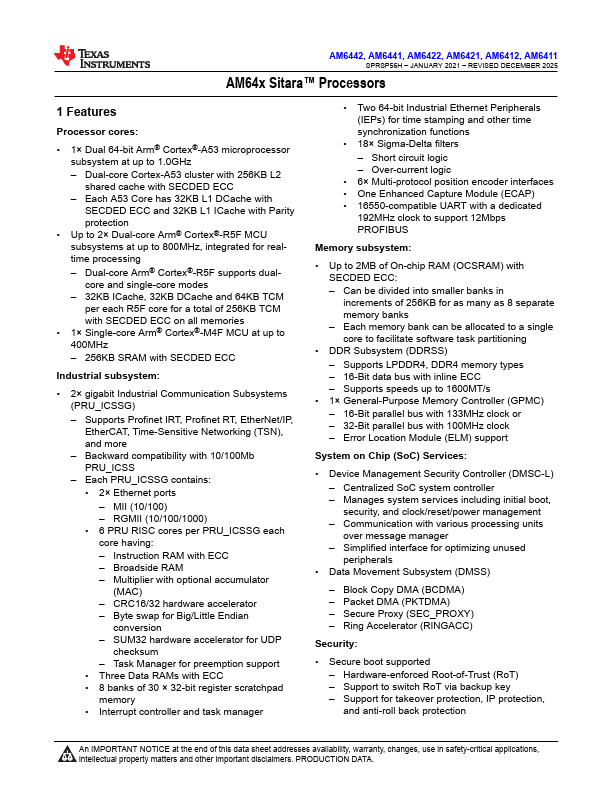

AM6412

Key Features

- 1× Dual 64-bit Arm® Cortex®-A53 microprocessor subsystem at up to 1.0GHz - Dual-core Cortex-A53 cluster with 256KB L2 shared cache with SECDED ECC - Each A53 Core has 32KB L1 DCache with SECDED ECC and 32KB L1 ICache with Parity protection

- Up to 2× Dual-core Arm® Cortex®-R5F MCU subsystems at up to 800MHz, integrated for realtime processing - Dual-core Arm® Cortex®-R5F supports dualcore and single-core modes - 32KB ICache, 32KB DCache and 64KB TCM per each R5F core for a total of 256KB TCM with SECDED ECC on all memories

- 1× Single-core Arm® Cortex®-M4F MCU at up to 400MHz - 256KB SRAM with SECDED ECC Industrial subsystem:

- 2× gigabit Industrial Communication Subsystems (PRU_ICSSG) - Supports Profinet IRT, Profinet RT, EtherNet/IP, EtherCAT, Time-Sensitive Networking (TSN), and more - Backward compatibility with 10/100Mb PRU_ICSS - Each PRU_ICSSG contains:

- 2× Ethernet ports - MII (10/100) - RGMII (10/100/1000)

- 6 PRU RISC cores per PRU_ICSSG each core having: - Instruction RAM with ECC - Broadside RAM - Multiplier with optional accumulator (MAC) - CRC16/32 hardware accelerator - Byte swap for Big/Little Endian conversion - SUM32 hardware accelerator for UDP checksum - Task Manager for preemption support

- Three Data RAMs with ECC

- 8 banks of 30 × 32-bit register scratchpad memory

- Interrupt controller and task manager

- Two 64-bit Industrial Ethernet Peripherals (IEPs) for time stamping and other time synchronization functions