CBTLV3857

CBTLV3857 is LOW-VOLTAGE 10-BIT FET BUS SWITCH manufactured by Texas Instruments.

D Enable Signal Is SSTL_2 patible D Flow-Through Architecture Optimizes PCB

Layout

D Designed for Use With 200 Mbit/s Double

Data-Rate (DDR) SDRAM Applications

D Switch On-State Resistance Is Designed to

Eliminate Series Resistor to DDR SDRAM

D Internal 10-kΩ Pulldown Resistors to

Ground on B Port

D Internal 50-kΩ Pullup Resistor on

Output-Enable Input

D Rail-to-Rail Switching on Data I/O Ports D Ioff Supports Partial-Power-Down Mode

Operation

D Latch-Up Performance Exceeds 100 m A Per

JESD 78, Class II

SN74CBTLV3857 LOWĆVOLTAGE 10ĆBIT FET BUS SWITCH WITH INTERNAL PULLDOWN RESISTORS

SCDS085E

- OCTOBER 1998

- REVISED OCTOBER 2003

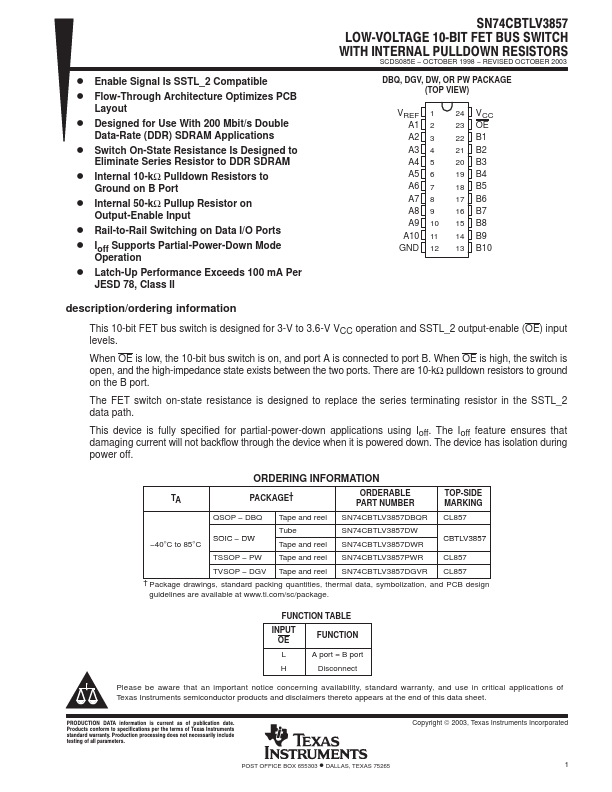

DBQ, DGV, DW, OR PW PACKAGE (TOP VIEW)

VREF 1 A1 2 A2 3 A3 4 A4 5 A5 6 A6 7 A7 8 A8 9 A9 10

A10 11 GND 12

24 VCC 23 OE 22 B1 21 B2 20 B3 19 B4 18 B5 17 B6 16 B7 15 B8 14 B9 13 B10 description/ordering information

This 10-bit FET bus switch is designed for 3-V to 3.6-V VCC operation and SSTL_2 output-enable (OE) input levels.

When OE is low, the 10-bit bus switch is on, and port A is connected to port B. When OE is high, the switch is open, and the high-impedance state exists between the two ports. There are 10-kΩ pulldown resistors to ground on the B port.

The FET switch on-state resistance is designed to replace the series terminating resistor in the SSTL_2 data path.

This device is fully specified for partial-power-down applications using Ioff. The Ioff feature ensures that damaging current will not backflow through the device when it is powered down. The device has isolation during power off.

ORDERING INFORMATION

PACKAGE†

ORDERABLE PART NUMBER

TOP-SIDE...