CD54HC195

Features

Description

- Asynchronous Master Reset

- J, K, (D) Inputs to First Stage

- Fully Synchronous Serial or Parallel Data Transfer

- Shift Right and Parallel Load Capability

- plementary Output From Last Stage

- Buffered Inputs

- CTy Lp=ic1a5l pf MF,ATXA==5205Mo HCz at VCC = 5V,

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- 10 LSTTL Loads

- Bus Driver Outputs

- - . . . 15 LSTTL Loads

- Wide Operating Temperature Range . . . -55o C to 125o C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction pared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: NIL = 30%, NIH = 30%of VCC at VCC = 5V

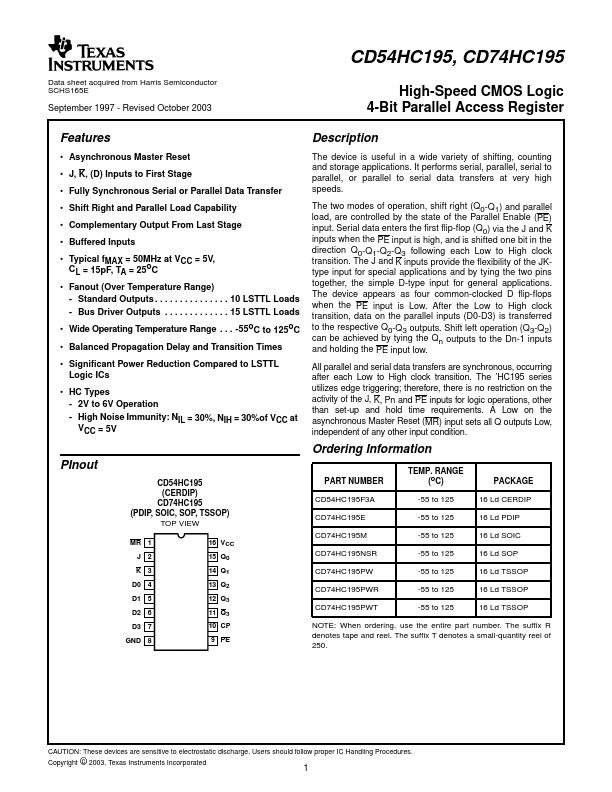

PInout

CD54HC195 (CERDIP)

CD74HC195 (PDIP, SOIC, SOP, TSSOP)

TOP VIEW

MR 1 J2 K3

D0 4 D1 5 D2 6 D3 7 GND 8

16 VCC 15 Q0 14 Q1 13 Q2 12 Q3 11 Q3 10 CP

9 PE

The device is useful in a wide variety of shifting, counting and storage applications. It performs serial, parallel, serial to parallel, or...