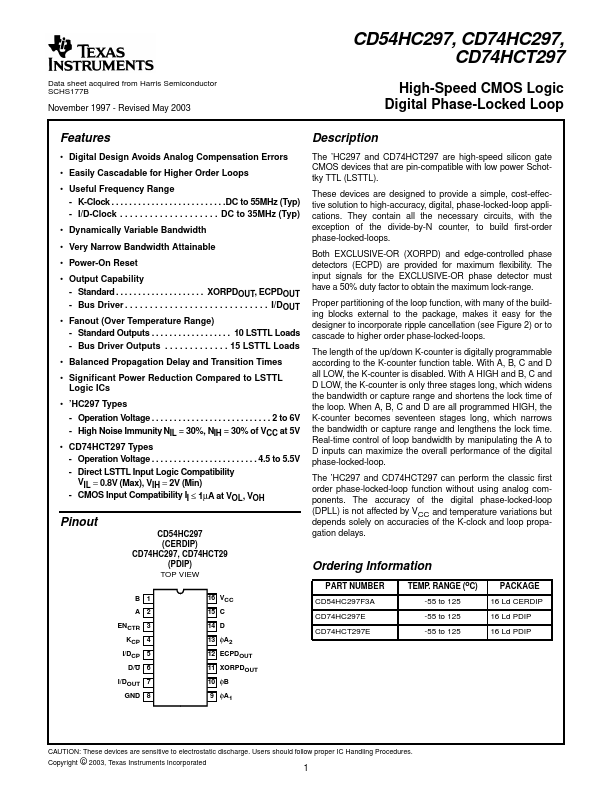

CD54HC297

Features

Description

- Digital Design Avoids Analog pensation Errors

- Easily Cascadable for Higher Order Loops

- Useful Frequency Range

- K-Clock

- -

- -

- .DC to 55MHz (Typ)

- I/D-Clock

- -

- - DC to 35MHz (Typ)

- Dynamically Variable Bandwidth

- Very Narrow Bandwidth Attainable

- Power-On Reset

- Output Capability

- Standard

- -

- - XORPDOUT, ECPDOUT

- Bus Driver

- -

- -

- . . . . I/DOUT

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- . . . 10 LSTTL Loads

- Bus Driver Outputs

- - . . . 15 LSTTL Loads

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction pared to LSTTL Logic ICs

- ’HC297 Types

- Operation Voltage

- -

- -

- . . 2 to 6V

- High Noise Immunity NIL = 30%, NIH = 30% of VCC at 5V

- CD74HCT297 Types

- Operation...