CD54HC4017

CD54HC4017 is Decade Counter/Divider manufactured by Texas Instruments.

D 2-V to 6-V Operation D Fully Static Operation D Buffered Inputs D mon Reset D Positive-Edge Clocking D Balanced Propagation Delay and Transition

Times

D High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5 V

D Packaged in Ceramic (F) DIP Package and

Also Available in Chip Form (H)

CD54HC4017 DECADE COUNTER/DIVIDER WITH TEN DECODED OUTPUTS

SGDS011

- MAY 1999

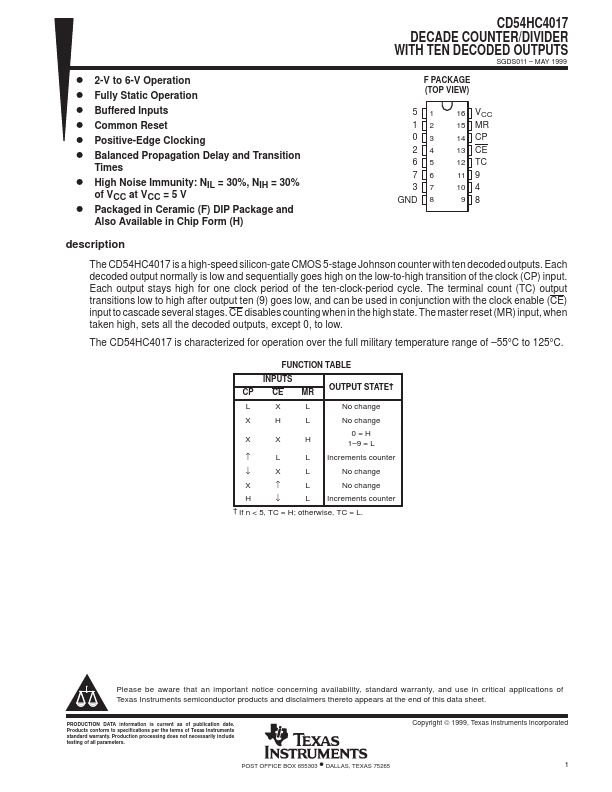

F PACKAGE (TOP VIEW)

51 12 03 24 65 76 37 GND 8

16 VCC 15 MR 14 CP 13 CE 12 TC 11 9 10 4 98 description

The CD54HC4017 is a high-speed silicon-gate CMOS 5-stage Johnson counter with ten decoded outputs. Each decoded output normally is low and sequentially goes high on the low-to-high transition of the clock (CP) input....