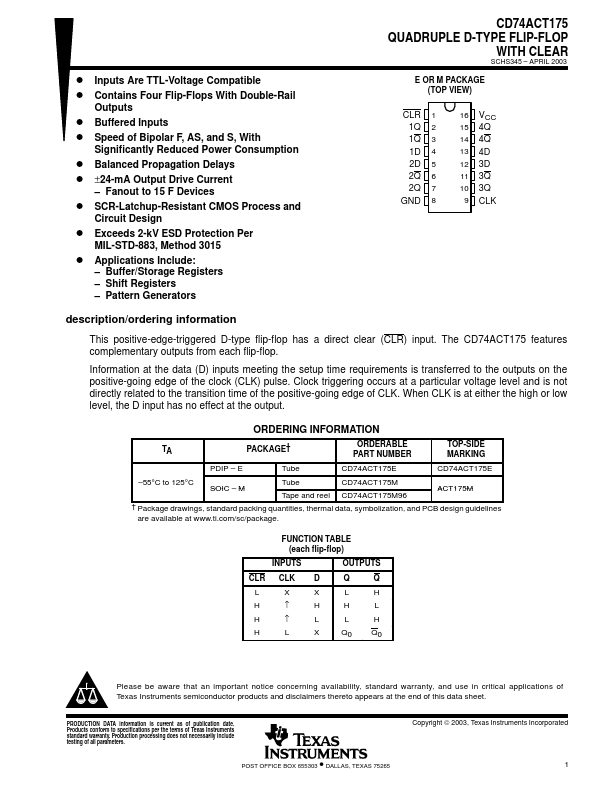

CD74ACT175

Key Features

- plementary outputs from each flip-flop

- Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going edge of CLK

- When CLK is at either the high or low level, the D input has no effect at the output