CD74HC126

CD74HC126 is High-Speed CMOS Logic manufactured by Texas Instruments.

Data sheet acquired from Harris Semiconductor SCHS144C

November 1997

- Revised September 2003

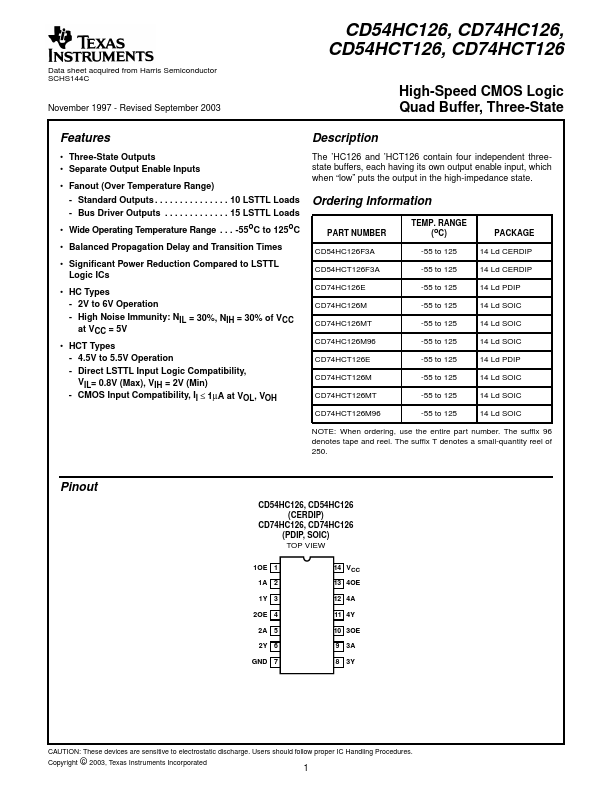

CD54HC126, CD74HC126, CD54HCT126, CD74HCT126

High-Speed CMOS Logic Quad Buffer, Three-State

[ /Title (CD74 HC126 , CD74 HCT12 6) /Subject (High Speed CMOS Logic Quad Buffer, Three State)

Features

Description

- Three-State Outputs

- Separate Output Enable Inputs

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- 10 LSTTL Loads

- Bus Driver Outputs

- - . . . 15 LSTTL Loads

- Wide Operating Temperature Range . . . -55o C to 125o C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction pared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

- HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic patibility, VIL= 0.8V (Max), VIH = 2V (Min)

- CMOS Input patibility, Il ≤ 1µA at VOL, VOH

The ’HC126 and ’HCT126 contain four independent threestate buffers, each having its own output enable input, which when “low” puts the output in the high-impedance state.

Ordering Information

PART NUMBER CD54HC126F3A CD54HCT126F3A CD74HC126E CD74HC126M CD74HC126MT CD74HC126M96 CD74HCT126E CD74HCT126M CD74HCT126MT CD74HCT126M96

TEMP. RANGE (o...