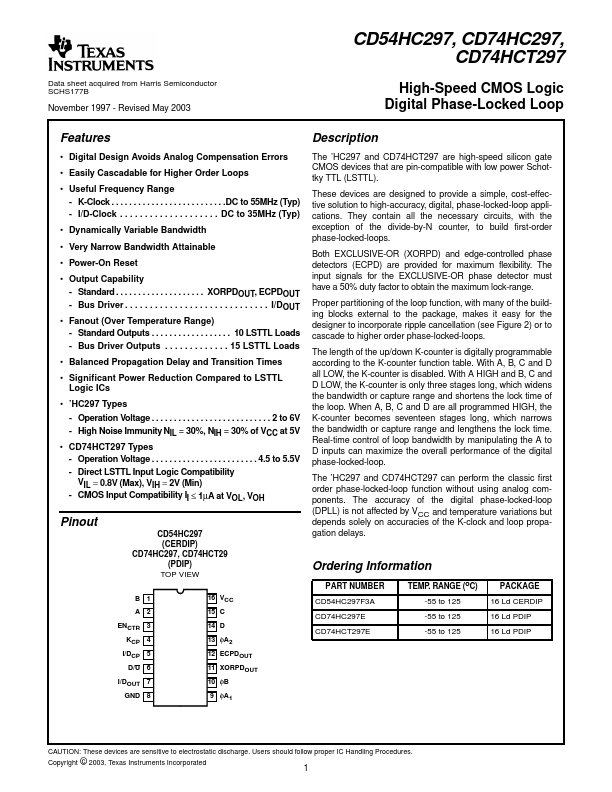

| Part | CD74HC297 |

|---|---|

| Description | Digital Phase-Locked Loop |

| Manufacturer | Texas Instruments |

| Size | 273.75 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| BUF04 | Analog Devices | Closed-Loop High Speed Buffer |

| TAS5805M | Texas Instruments | Closed-Loop Class-D Audio Amplifier |

| TAS5825M | Texas Instruments | Closed-Loop Class-D Audio Amplifier |