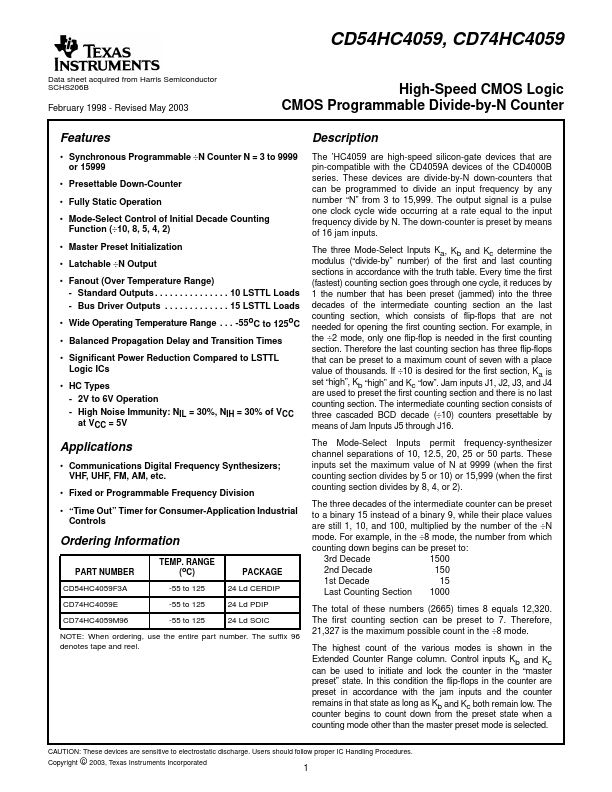

CD74HC4059 Overview

Description

Synchronous Programmable ÷N Counter N = 3 to 9999 or 15999 - Presettable Down-Counter - Fully Static Operation - Mode-Select Control of Initial Decade Counting Function (÷10, 8, 5, 4, 2) - Master Preset Initialization - Latchable ÷N Output - Fanout (Over Temperature Range) - Standard Outputs. Wide Operating Temperature Range.