CDC5806

Description

The CDC5806 is a clock generator which synthesizes video clocks, audio clocks, CPU clock, ASIC clock, USB clock, and a memory card clock from a 54-MHz system clock. Three phase-locked loops (PLLs) are used to generate the different frequencies from the system clock.

Key Features

- High Performance Clock Generator

- Clock Input compatible With LVCMOS/LVTTL

- Requires a 54-MHz Input Clock to Generate Multiple Output Frequencies

- Low Jitter for Clock Distribution

- Operates From Single 3.3-V Supply

- Low Peak-to-Peak Period Jitter (150 ps Max)

- PLLs Are Powered Down, if No Valid REF_IN Clock (< 5 MHz) is Detected or the VDD is Below 2 V

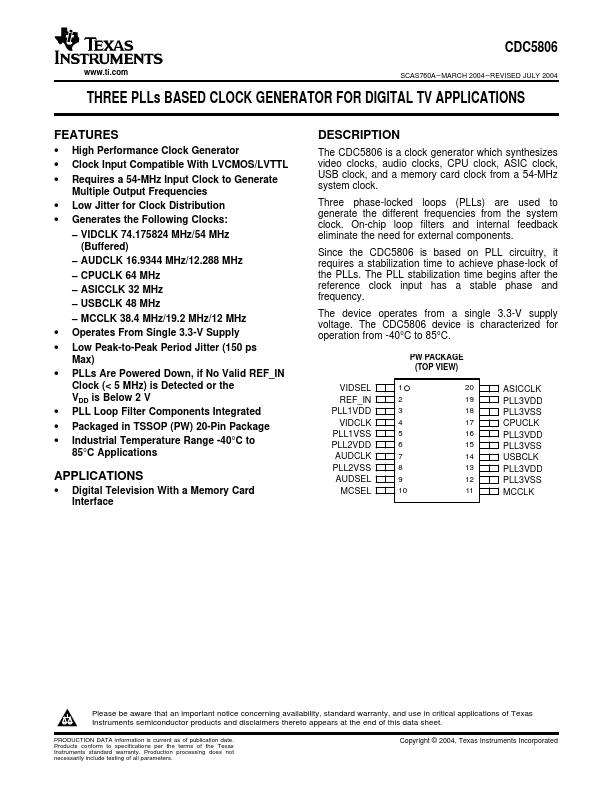

- Packaged in TSSOP (PW) 20-Pin Package

- Industrial Temperature Range -40°C to 85°C Applications