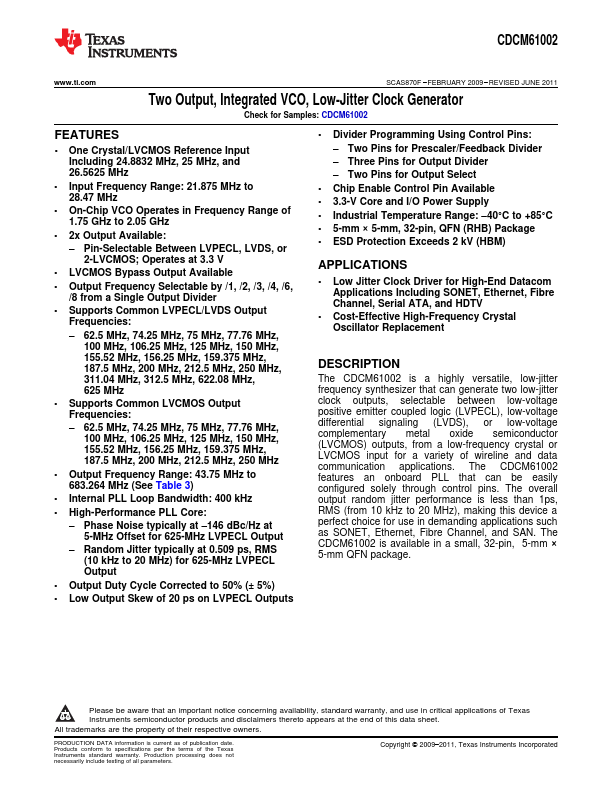

CDCM61002

CDCM61002 is Low-Jitter Clock Generator manufactured by Texas Instruments.

FEATURES

- 2 One Crystal/LVCMOS Reference Input Including 24.8832 MHz, 25 MHz, and 26.5625 MHz

- Input Frequency Range: 21.875 MHz to 28.47 MHz

- On-Chip VCO Operates in Frequency Range of 1.75 GHz to 2.05 GHz

- 2x Output Available:

- Pin-Selectable Between LVPECL, LVDS, or 2-LVCMOS; Operates at 3.3 V

- LVCMOS Bypass Output Available

- Output Frequency Selectable by /1, /2, /3, /4, /6, /8 from a Single Output Divider

- Supports mon LVPECL/LVDS Output Frequencies:

- 62.5 MHz, 74.25 MHz, 75 MHz, 77.76 MHz, 100 MHz, 106.25 MHz, 125 MHz, 150 MHz, 155.52 MHz, 156.25 MHz, 159.375 MHz, 187.5 MHz, 200 MHz, 212.5 MHz, 250 MHz, 311.04 MHz, 312.5 MHz, 622.08 MHz, 625 MHz

- Supports mon LVCMOS Output Frequencies:

- 62.5 MHz, 74.25 MHz, 75 MHz, 77.76 MHz, 100 MHz, 106.25 MHz, 125 MHz, 150 MHz, 155.52 MHz, 156.25 MHz, 159.375 MHz, 187.5 MHz, 200 MHz, 212.5 MHz, 250 MHz

- Output Frequency Range: 43.75 MHz to 683.264 MHz (See Table 3)

- Internal PLL Loop Bandwidth: 400 k Hz

- High-Performance PLL Core:

- Phase Noise typically at

- 146 d Bc/Hz at 5-MHz Offset for 625-MHz LVPECL Output

- Random Jitter typically at 0.509 ps, RMS (10 k Hz to 20 MHz) for 625-MHz LVPECL Output

- Output Duty Cycle Corrected to 50% (± 5%)

- Low Output Skew of 20 ps on LVPECL Outputs

- Divider Programming Using Control Pins:

- Two Pins for Prescaler/Feedback Divider

- Three Pins for Output Divider

- Two Pins for Output Select

- Chip Enable Control Pin Available

- 3.3-V Core and I/O Power Supply

- Industrial Temperature Range:

- 40°C to +85°C

- 5-mm × 5-mm, 32-pin, QFN (RHB) Package

- ESD Protection Exceeds 2 k V (HBM)

APPLICATIONS

- Low Jitter Clock Driver for High-End Data Applications Including SONET, Ethernet, Fibre Channel, Serial ATA, and HDTV

- Cost-Effective High-Frequency Crystal Oscillator Replacement

DESCRIPTION

The CDCM61002 is a highly versatile, low-jitter frequency synthesizer that can generate two low-jitter clock outputs, selectable between low-voltage positive emitter coupled logic (LVPECL),...