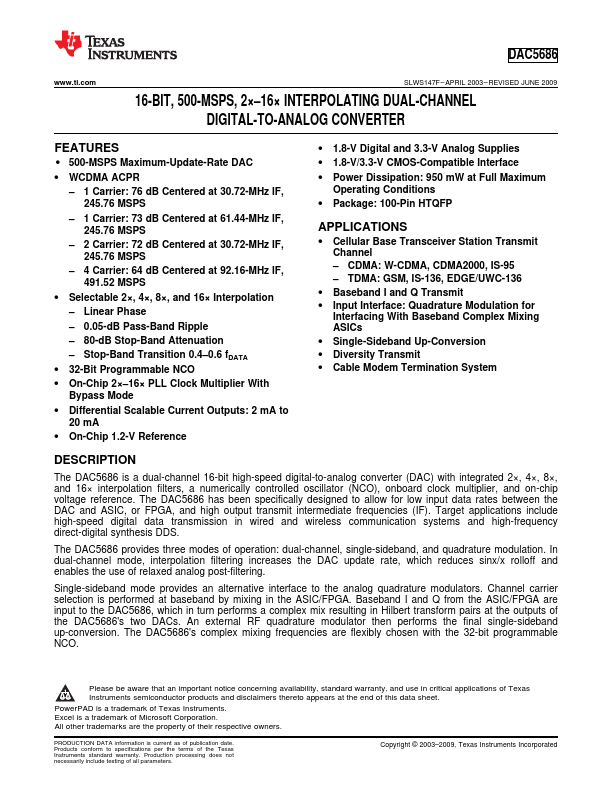

DAC5686

FEATURES

- 234 500-MSPS Maximum-Update-Rate DAC

- WCDMA ACPR

- 1 Carrier: 76 d B Centered at 30.72-MHz IF, 245.76 MSPS

- 1 Carrier: 73 d B Centered at 61.44-MHz IF, 245.76 MSPS

- 2 Carrier: 72 d B Centered at 30.72-MHz IF, 245.76 MSPS

- 4 Carrier: 64 d B Centered at 92.16-MHz IF, 491.52 MSPS

- Selectable 2×, 4×, 8×, and 16× Interpolation

- Linear Phase

- 0.05-d B Pass-Band Ripple

- 80-d B Stop-Band Attenuation

- Stop-Band Transition 0.4- 0.6 f DATA

- 32-Bit Programmable NCO

- On-Chip 2×- 16× PLL Clock Multiplier With

Bypass Mode

- Differential Scalable Current Outputs: 2 m A to

20 m A

- On-Chip 1.2-V Reference

- 1.8-V Digital and 3.3-V Analog Supplies

- 1.8-V/3.3-V CMOS-patible Interface

- Power Dissipation: 950 m W at Full Maximum

Operating Conditions

- Package: 100-Pin HTQFP

APPLICATIONS

- Cellular Base Transceiver Station Transmit Channel

- CDMA: W-CDMA, CDMA2000, IS-95

- TDMA: GSM, IS-136, EDGE/UWC-136

- Baseband I and Q Transmit

- Input Interface: Quadrature Modulation for

Interfacing With...