DRA783

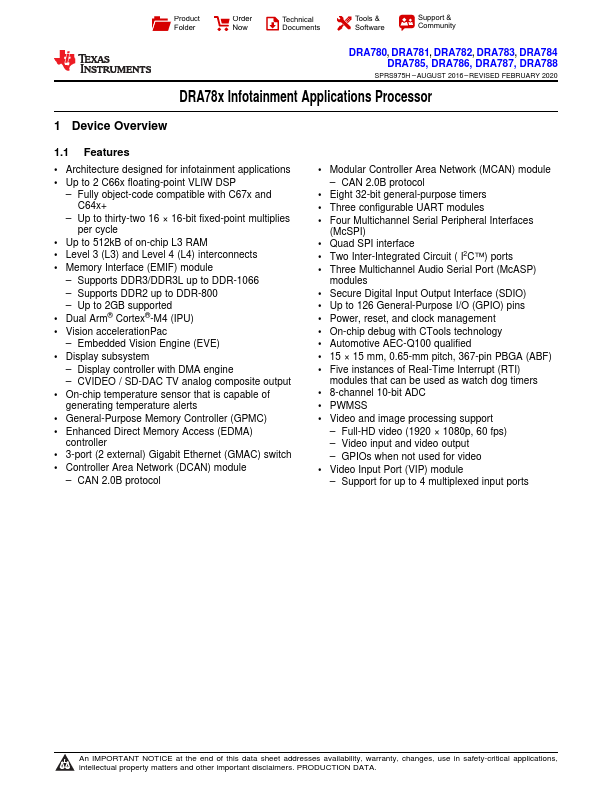

Key Features

- Architecture designed for infotainment applications

- Up to 2 C66x floating-point VLIW DSP

- Up to thirty-two 16 × 16-bit fixed-point multiplies per cycle

- Up to 512kB of on-chip L3 RAM

- Memory Interface (EMIF) module

- Supports DDR3/DDR3L up to DDR-1066 - Supports DDR2 up to DDR-800 - Up to 2GB supported

- Dual Arm® Cortex®-M4 (IPU)

- Vision accelerationPac - Embedded Vision Engine (EVE)

- Display subsystem - Display controller with DMA engine - CVIDEO / SD-DAC TV analog posite output

- On-chip temperature sensor that is capable of generating temperature alerts