DS280MB810

DS280MB810 is Low Power 28 Gbps 8 Channel Linear Repeater manufactured by Texas Instruments.

Features

- 1 Octal-Channel Multi-Protocol Linear Equalizer Supporting up to 28 Gbaud Interfaces

- Integrated 2x2 Cross-point with Pin or Register Control for Mux, Fanout, and Signal Crossing Applications

- Low Power Consumption: 93 m W / Channel (Typical)

- No Heat Sink Required

- Linear Equalization for Seamless Support of Link Training, Auto-Negotiation, and FEC Pass Through

- Extends Channel Reach by 17d B+ Beyond Normal ASIC-to-ASIC Capability at 14 GHz

- Ultra-Low Latency: 100 ps (Typical)

- Low Additive Random Jitter

- Small 8 mm x 13 mm BGA Package with Integrated RX AC Coupling Capacitors for Easy Flow-Through Routing

- Unique Pinout Allows Routing High-Speed Signals Underneath the Package

- Pin-patible Retimer with Cross-point Available

- Single 2.5-V ±5% Power Supply

- - 40°C to +85°C Operating Temperature Range

2 Applications

- Backplane and Mid-Plane Signal Distribution Plus Equalization

- Mux and De-Mux for Failover Redundancy

- Front-Port Eye Opener Plus Signal Distribution for Switching Between Ports

3 Description

The DS280MB810 is an extremely low-power, highperformance eight-channel linear equalizer supporting multi-rate, multi-protocol interfaces up to 28 Gbaud. It is used to extend the reach and improve the robustness of high-speed serial links for backplane, front-port, and chip-to-chip applications.

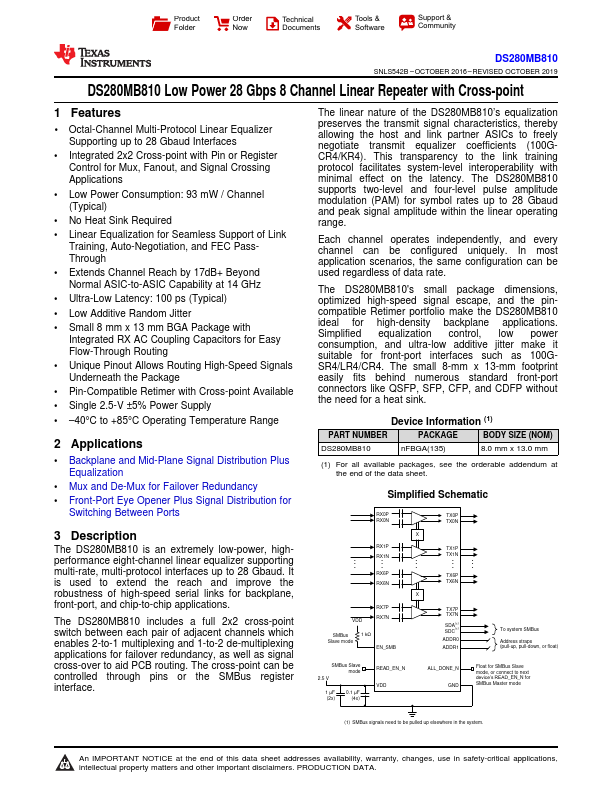

The DS280MB810 includes a full 2x2 cross-point switch between each pair of adjacent channels which enables 2-to-1 multiplexing and 1-to-2 de-multiplexing applications for failover redundancy, as well as signal cross-over to aid PCB routing. The cross-point can be controlled through pins or the SMBus register interface.

The linear nature of the DS280MB810’s equalization preserves the transmit signal characteristics, thereby allowing the host and link partner ASICs to freely negotiate transmit equalizer coefficients (100GCR4/KR4). This transparency to the link training protocol facilitates system-level interoperability with minimal effect on the latency....