DS90LT012A

Description

The DS90LV012A and DS90LT012A are single CMOS differential line receivers designed for applications requiring ultra low power dissipation, low noise, and high data rates.

Key Features

- >400 Mbps (200 MHz) switching rates

- 100 ps differential skew (typical)

- 3.5 ns maximum propagation delay

- Integrated line termination resistor (102Ω typical)

- Single 3.3V power supply design (2.7V to 3.6V range)

- Power down high impedance on LVDS inputs

- Accepts small swing (350 mV typical) differential signal levels

- LVDS receiver inputs accept LVDS/BLVDS/LVPECL inputs

- Supports open, short and terminated input fail- safe

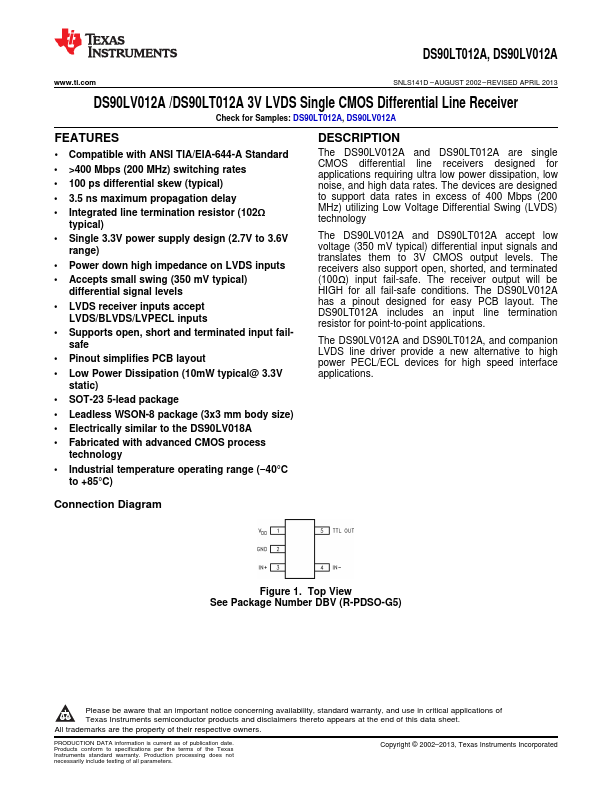

- Pinout simplifies PCB layout