HJ4060

Overview

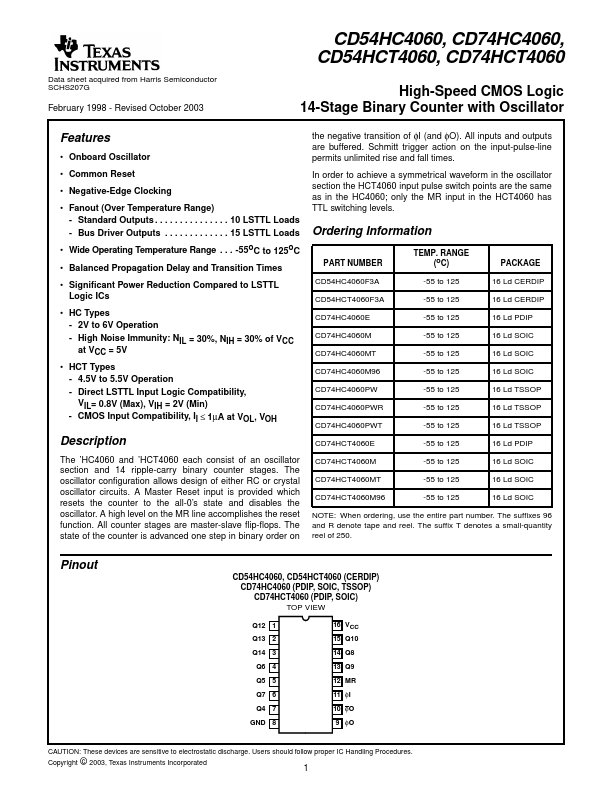

The ’HC4060 and ’HCT4060 each consist of an oscillator section and 14 ripple-carry binary counter stages. The oscillator configuration allows design of either RC or crystal oscillator circuits.

- Onboard Oscillator

- Common Reset

- Negative-Edge Clocking

- Wide Operating Temperature Range . . . -55oC to 125oC

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types - 2V to 6V Operation - High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

- HCT Types - 4.5V to 5.5V Operation - Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min) - CMOS Input Compatibility, Il ≤ 1µA at VOL, VOH