LMC568

LMC568 is Low Power Phase-Locked Loop manufactured by Texas Instruments.

FEATURES

- 2 Demodulates ±15% Deviation FM/FSK Signals

- Carrier Detect Output with Hysteresis

- Operation to 500 k Hz Input Frequency

- Low THD- 0.5% Typ. for ±10% Deviation

- 2V to 9V Supply Voltage Range

- Low Supply Current Drain

DESCRIPTION

The LMC568 is an amplitude-linear phase-locked loop consisting of a linear VCO, fully balanced phase detectors, and a carrier detect output. LMCMOS technology is employed for high performance with low power consumption.

The VCO has a linearized control range of ±30% to allow demodulation of FM and FSK signals. Carrier detect is indicated when the PLL is locked to an input signal greater than 26 m Vrms. LMC568 applications include FM SCA and TV second audio program decoders, FSK data demodulators, and voice pagers.

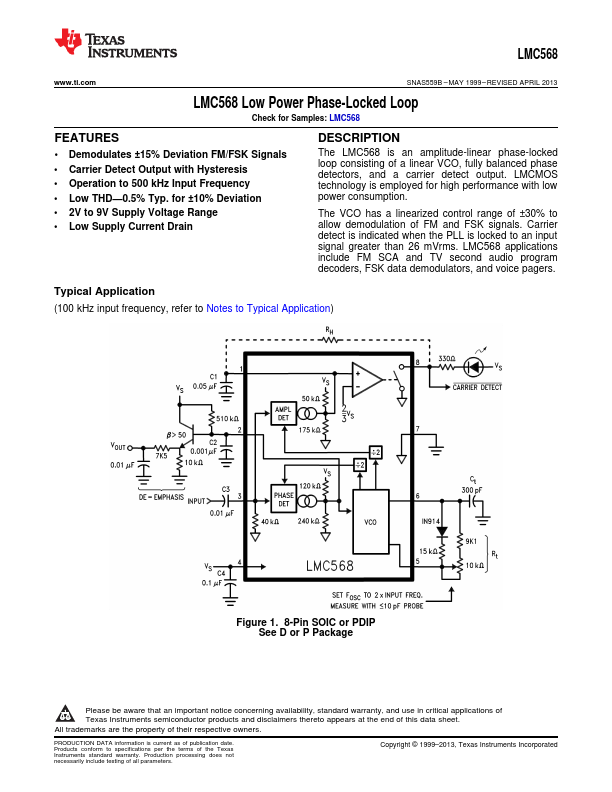

Typical Application (100 k Hz input frequency, refer to Notes to Typical Application)

Figure 1. 8-Pin SOIC or PDIP See D or P Package

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999- 2013, Texas Instruments Incorporated

SNAS559B

- MAY 1999

- REVISED APRIL 2013

.ti.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings(1)(2)

Input Voltage, Pin 3

Supply Voltage, Pin 4

Output Voltage, Pin 8

Voltage at All Other Pins

Output Current, Pin 8

Package Dissipation

Operating Temperature Range (TA) Storage Temperature Range

Soldering...