LMK04001

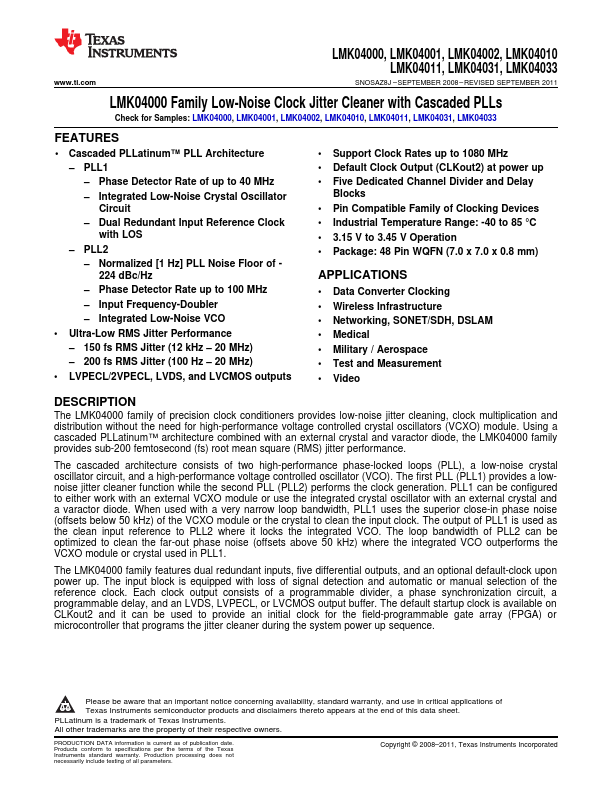

LMK04001 is Family Low-Noise Clock Jitter Cleaner manufactured by Texas Instruments.

- Part of the LMK04000 comparator family.

- Part of the LMK04000 comparator family.

FEATURES

- 23 Cascaded PLLatinum™ PLL Architecture

- PLL1

- Phase Detector Rate of up to 40 MHz

- Integrated Low-Noise Crystal Oscillator Circuit

- Dual Redundant Input Reference Clock with LOS

- PLL2

- Normalized [1 Hz] PLL Noise Floor of 224 d Bc/Hz

- Phase Detector Rate up to 100 MHz

- Input Frequency-Doubler

- Integrated Low-Noise VCO

- Ultra-Low RMS Jitter Performance

- 150 fs RMS Jitter (12 k Hz

- 20 MHz)

- 200 fs RMS Jitter (100 Hz

- 20 MHz)

- LVPECL/2VPECL, LVDS, and LVCMOS outputs

- Support Clock Rates up to 1080 MHz

- Default Clock Output (CLKout2) at power up

- Five Dedicated Channel Divider and Delay

Blocks

- Pin patible Family of Clocking Devices

- Industrial Temperature Range: -40 to 85 °C

- 3.15 V to 3.45 V Operation

- Package: 48 Pin WQFN (7.0 x 7.0 x 0.8 mm)

APPLICATIONS

- Data Converter Clocking

- Wireless Infrastructure

- Networking, SONET/SDH, DSLAM

- Medical

- Military / Aerospace

- Test and Measurement

- Video

DESCRIPTION

The LMK04000 family of precision clock conditioners provides low-noise jitter cleaning, clock multiplication and distribution without the need for high-performance voltage controlled crystal oscillators (VCXO) module. Using a cascaded PLLatinum™ architecture bined with an external crystal and varactor diode, the LMK04000 family provides sub-200 femtosecond (fs) root mean square (RMS) jitter performance.

The cascaded architecture consists of two high-performance phase-locked loops (PLL), a low-noise crystal oscillator circuit, and a high-performance voltage controlled oscillator (VCO). The first PLL (PLL1) provides a lownoise jitter cleaner function while the second PLL (PLL2) performs the clock generation. PLL1 can be configured to either work with an external VCXO module or use the integrated crystal oscillator with an external crystal and a varactor diode. When used with a very narrow loop bandwidth, PLL1 uses the superior close-in phase noise (offsets below 50 k Hz) of the VCXO module or the crystal to clean the input...