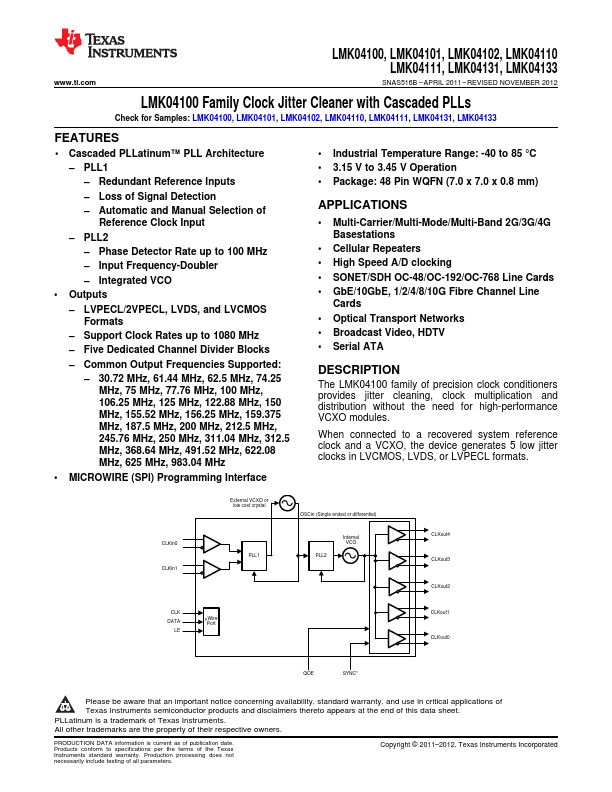

LMK04100 Description

The LMK04100 family of precision clock conditioners provides jitter cleaning, clock multiplication and distribution without the need for high-performance VCXO modules. When connected to a recovered system reference clock and a VCXO, the device generates 5 low jitter clocks in LVCMOS, LVDS, or LVPECL formats. CLKin0 CLKin1 External VCXO or low cost crystal PLL1 OSCin (Single ended or differential) PLL2 Internal VCO...

LMK04100 Key Features

- 23 Cascaded PLLatinum™ PLL Architecture

- Redundant Reference Inputs

- Loss of Signal Detection

- Automatic and Manual Selection of Reference Clock Input

- Phase Detector Rate up to 100 MHz

- Input Frequency-Doubler

- Integrated VCO

- Outputs

- LVPECL/2VPECL, LVDS, and LVCMOS Formats

- Support Clock Rates up to 1080 MHz