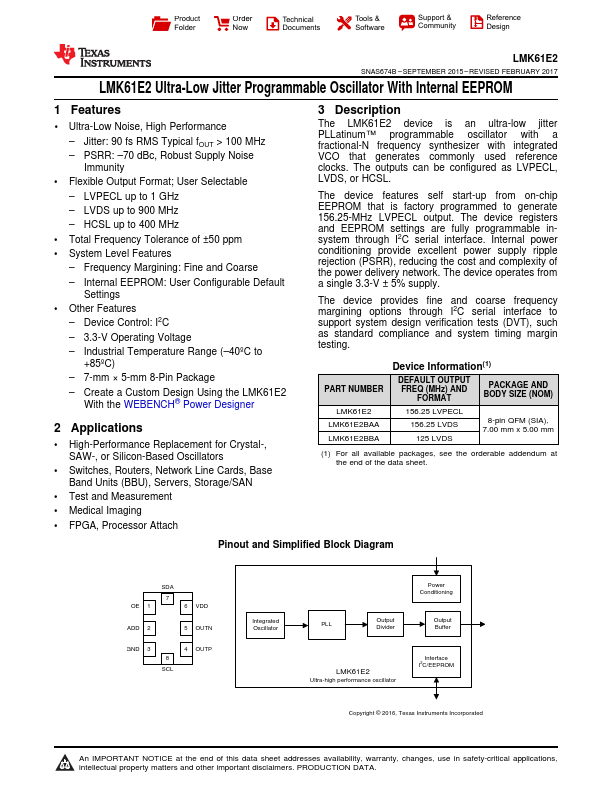

LMK61E2 Description

The LMK61E2 device is an ultra-low jitter PLLatinum™ programmable oscillator with a fractional-N frequency synthesizer with integrated VCO that generates monly used reference clocks. The outputs can be configured as LVPECL, LVDS, or HCSL.

LMK61E2 Key Features

- 1 Ultra-Low Noise, High Performance

- Jitter: 90 fs RMS Typical fOUT > 100 MHz

- PSRR: -70 dBc, Robust Supply Noise Immunity

- Flexible Output Format; User Selectable

- LVPECL up to 1 GHz

- LVDS up to 900 MHz

- HCSL up to 400 MHz

- Total Frequency Tolerance of ±50 ppm

- System Level Features

- Frequency Margining: Fine and Coarse

LMK61E2 Applications

- High-Performance Replacement for Crystal-, SAW-, or Silicon-Based Oscillators