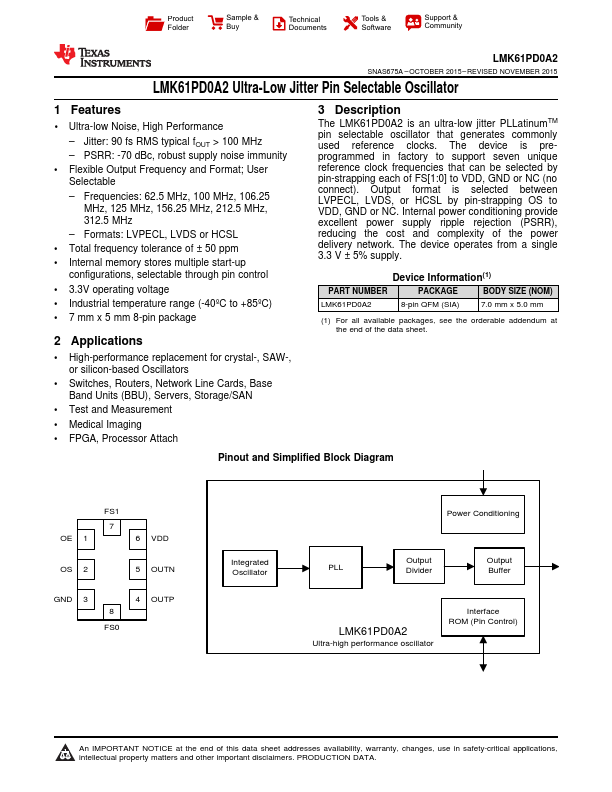

LMK61PD0A2 Description

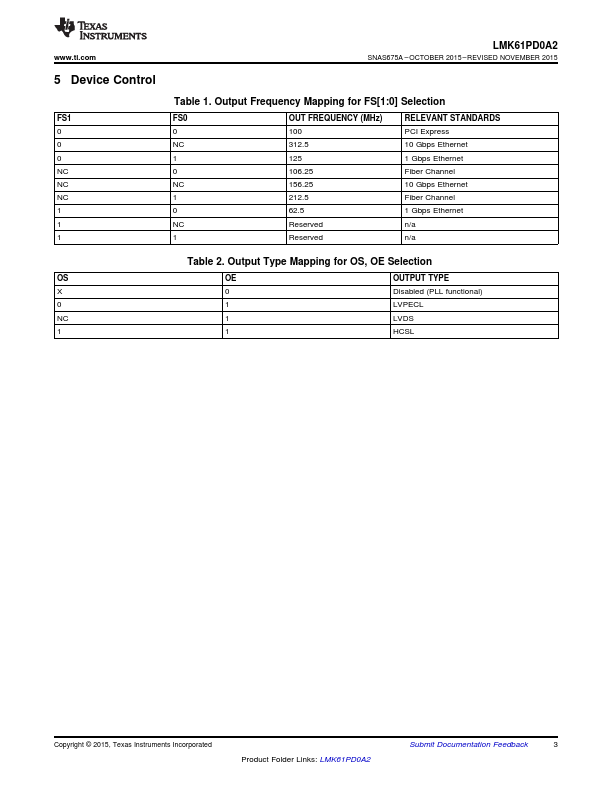

The LMK61PD0A2 is an ultra-low jitter PLLatinumTM pin selectable oscillator that generates monly used reference clocks. The device is preprogrammed in factory to support seven unique reference clock frequencies that can be selected by pin-strapping each of FS[1:0] to VDD, GND or NC (no connect). Output format is selected between LVPECL, LVDS, or HCSL by pin-strapping OS to VDD, GND or NC.

LMK61PD0A2 Key Features

- 1 Ultra-low Noise, High Performance

- Jitter: 90 fs RMS typical fOUT > 100 MHz

- PSRR: -70 dBc, robust supply noise immunity

- Flexible Output Frequency and Format; User Selectable

- Formats: LVPECL, LVDS or HCSL

- Total frequency tolerance of ± 50 ppm

- Internal memory stores multiple start-up

- 3.3V operating voltage

- Industrial temperature range (-40ºC to +85ºC)

- 7 mm x 5 mm 8-pin package

LMK61PD0A2 Applications

- High-performance replacement for crystal-, SAW-, or silicon-based Oscillators