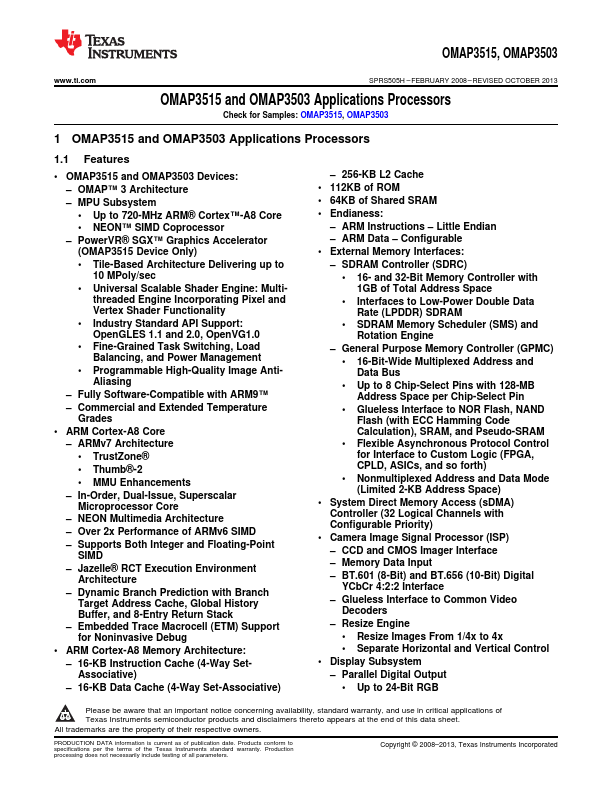

OMAP3515

Key Features

- 256-KB L2 Cache

- 112KB of ROM

- 64KB of Shared SRAM

- External Memory Interfaces: – SDRAM Controller (SDRC)

- 16- and 32-Bit Memory Controller with 1GB of Total Address Space

- Interfaces to Low-Power Double Data Rate (LPDDR) SDRAM

- SDRAM Memory Scheduler (SMS) and Rotation Engine

- 16-Bit-Wide Multiplexed Address and Data Bus

- Up to 8 Chip-Select Pins with 128-MB Address Space per Chip-Select Pin

- Glueless Interface to NOR Flash, NAND Flash (with ECC Hamming Code Calculation), SRAM, and Pseudo-SRAM