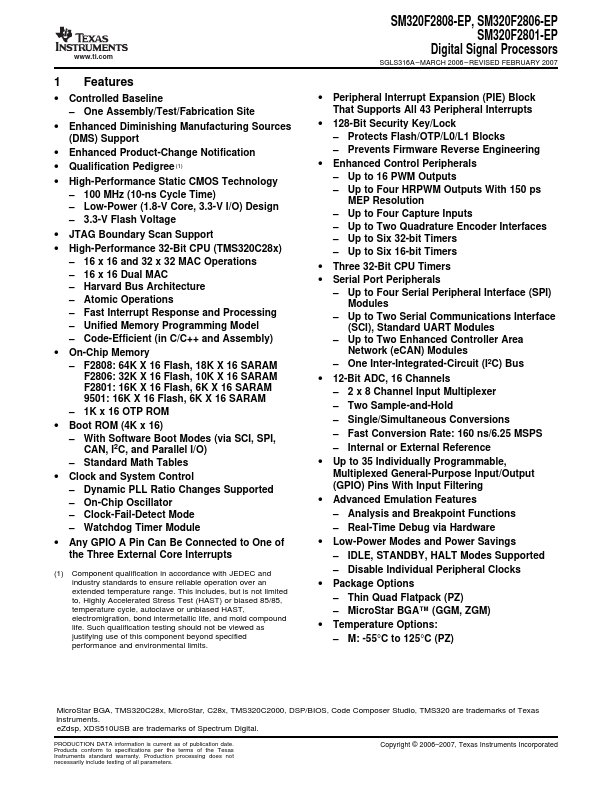

SM320F2806-EP Overview

Key Features

- Controlled Baseline – One Assembly/Test/Fabrication Site

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree(1)

- High-Performance Static CMOS Technology – 100 MHz (10-ns Cycle Time) – Low-Power (1.8-V Core, 3.3-V I/O) Design – 3.3-V Flash Voltage

- JTAG Boundary Scan Support

- Boot ROM (4K x

- With Software Boot Modes (via SCI, SPI, CAN, I2C, and Parallel I/O) – Standard Math Tables

- Clock and System Control – Dynamic PLL Ratio Changes Supported – On-Chip Oscillator – Clock-Fail-Detect Mode – Watchdog Timer Module

- Peripheral Interrupt Expansion (PIE) Block That Supports All 43 Peripheral Interrupts