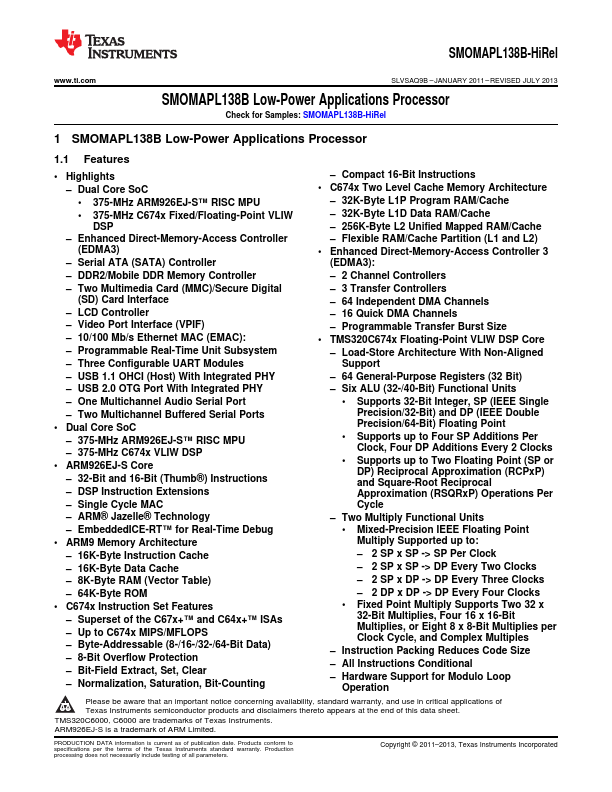

SMOMAPL138B-HIREL Overview

Key Features

- Highlights – Compact 16-Bit Instructions – Dual Core SoC

- C674x Two Level Cache Memory Architecture

- 375-MHz ARM926EJ-S™ RISC MPU – 32K-Byte L1P Program RAM/Cache

- Supports 32-Bit Integer, SP (IEEE Single – Two Multichannel Buffered Serial Ports

- Dual Core SoC – 375-MHz ARM926EJ-S™ RISC MPU – 375-MHz C674x VLIW DSP