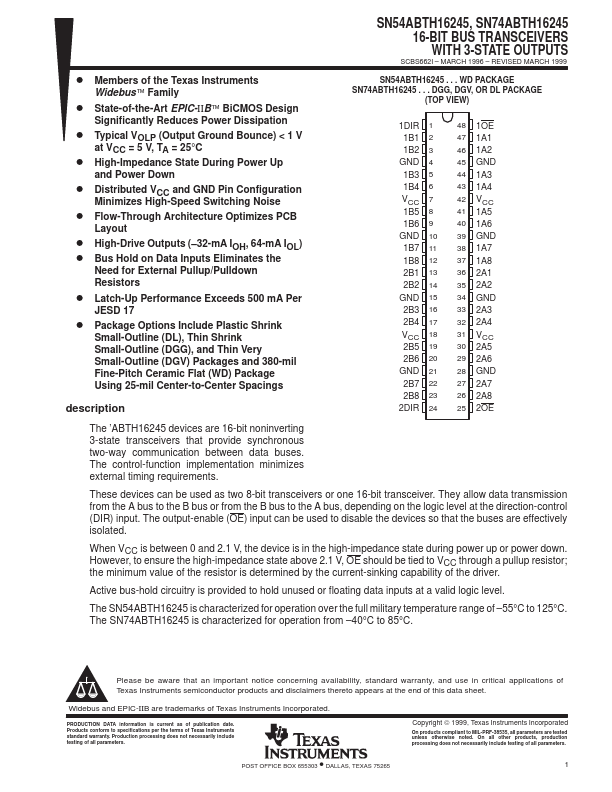

| Part | SN54ABTH16245 |

|---|---|

| Description | 16-BIT BUS TRANSCEIVERS |

| Manufacturer | Texas Instruments |

| Size | 531.43 KB |

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| No distributor offers were returned for this part. | |||

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| SP3232 | Sipex | 3.3V / 1000 Kbps RS-232 Transceivers |

| MAX3490 | Maxim Integrated | True RS-485/RS-422 Transceivers |

| SP3232E | MaxLinear | True 3.0V to 5.5V RS-232 Transceivers |