SN54AS74A

SN54AS74A is Dual Positive-Edge-Triggered D-Type Flip-Flops manufactured by Texas Instruments.

- Part of the SN54ALS74A comparator family.

- Part of the SN54ALS74A comparator family.

description

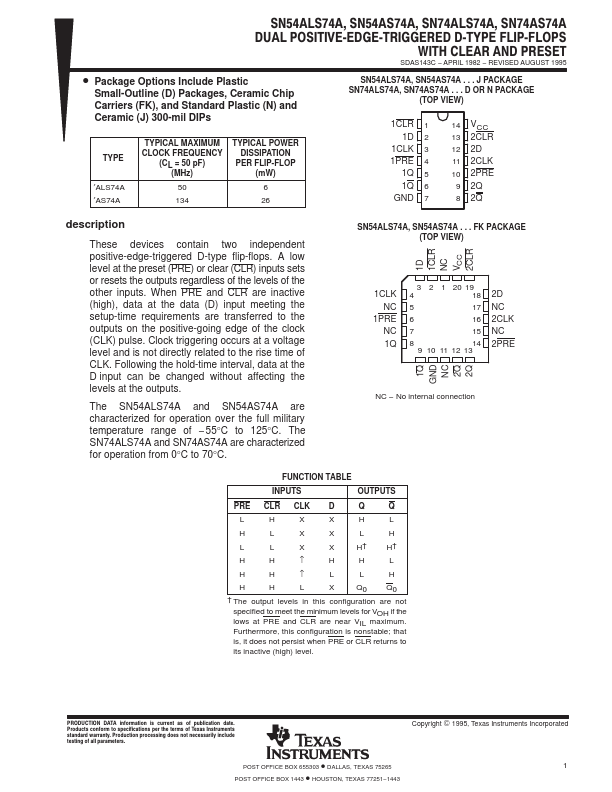

These devices contain two independent positive-edge-triggered D-type flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup-time requirements are transferred to the outputs on the positive-going edge of the clock (CLK) pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of CLK. Following the hold-time interval, data at the D input can be changed without affecting the levels at the outputs.

The SN54ALS74A and SN54AS74A are characterized for operation over the full military temperature range of

- 55°C to 125°C. The SN74ALS74A and SN74AS74A are characterized for operation from 0°C to 70°C.

SN54ALS74A, SN54AS74A . . . FK PACKAGE (TOP VIEW)

1D 1CLR NC VCC 2CLR

1CLK NC

1PRE NC 1Q

3 2 1 20 19

9 10 11 12 13

2D NC 2CLK NC 2PRE

1Q GND

NC 2Q 2Q

- No internal connection

FUNCTION TABLE

INPUTS

OUTPUTS

PRE CLR CLK...