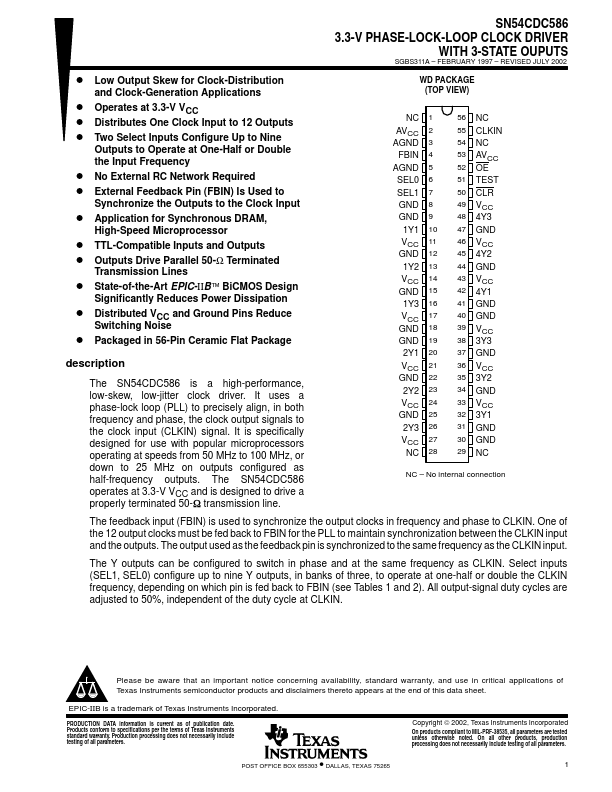

| Part | SN54CDC586 |

|---|---|

| Description | 3.3-V PHASE-LOCK-LOOP CLOCK DRIVER |

| Manufacturer | Texas Instruments |

| Size | 136.89 KB |

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| No distributor offers were returned for this part. | |||

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| OB3375 | On-Bright | High performance buck LED driver |

| NSi6602 | NOVOSENSE | High Reliability Isolated Dual-Channel Gate Driver |

| BP2861X | BPS | step-down LED constant current driver |