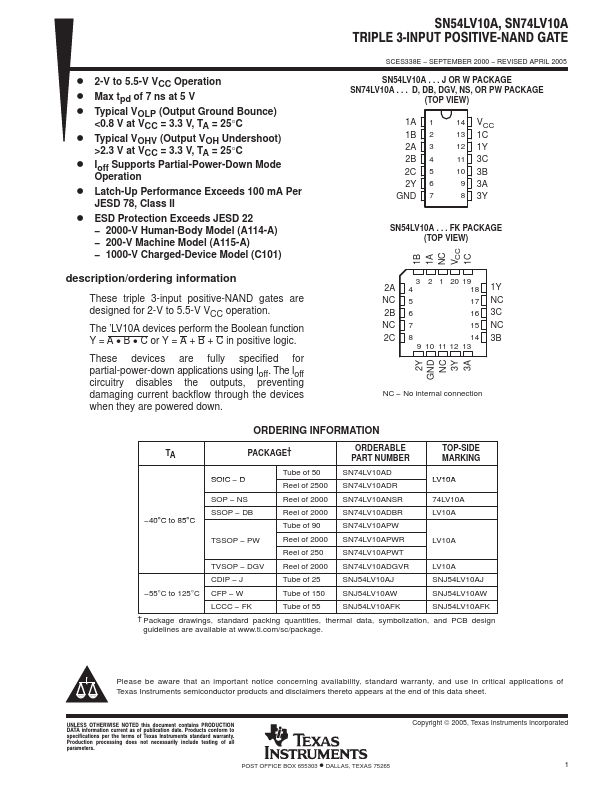

| Part | SN54LV10A |

|---|---|

| Description | TRIPLE 3-INPUT POSITIVE-NAND GATE |

| Manufacturer | Texas Instruments |

| Size | 921.64 KB |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| NSi6602 | NOVOSENSE | High Reliability Isolated Dual-Channel Gate Driver |

| NSi6801 | NOVOSENSE | Single-Channel Isolated Gate Driver |

| FD2103 | Fortior | 180V Half-Bridge Gate Driver |