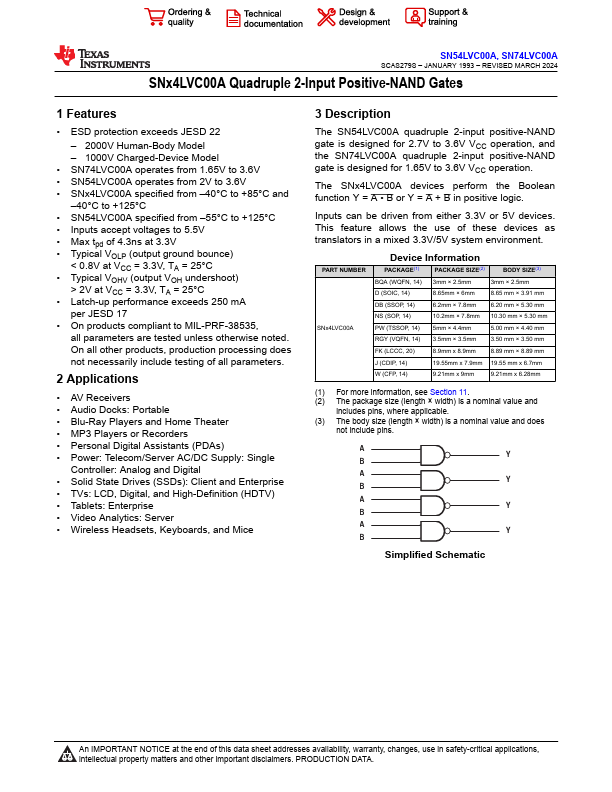

SN54LVC00A Overview

Key Specifications

Output Type (varies by manufacturer): TTL

Description

The SN54LVC00A quadruple 2-input positive-NAND gate is designed for 2.7V to 3.6V VCC operation, and the SN74LVC00A quadruple 2-input positive-NAND gate is designed for 1.65V to 3.6V VCC operation. The SNx4LVC00A devices perform the Boolean function Y = A - B or Y = A + B in positive logic.

Key Features

- ESD protection exceeds JESD 22 – 2000V Human-Body Model – 1000V Charged-Device Model

- Inputs accept voltages to 5.5V

- Max tpd of 4.3ns at 3.3V

- Typical VOLP (output ground bounce) < 0.8V at VCC = 3.3V, TA = 25°C

- Typical VOHV (output VOH undershoot) > 2V at VCC = 3.3V, TA = 25°C