SN65LVDS100

Overview

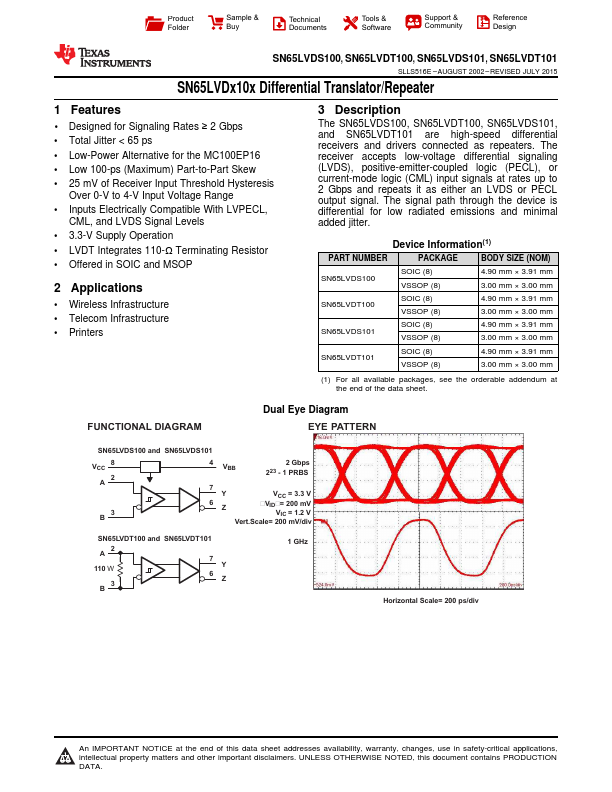

The SN65LVDS100, SN65LVDT100, SN65LVDS101, and SN65LVDT101 are high-speed differential receivers and drivers connected as repeaters. The receiver accepts low-voltage differential signaling (LVDS), positive-emitter-coupled logic (PECL), or current-mode logic (CML) input signals at rates up to 2 Gbps and repeats it as either an LVDS or PECL output signal.

- 1 Designed for Signaling Rates ≥ 2 Gbps

- Total Jitter < 65 ps

- Low-Power Alternative for the MC100EP16

- Low 100-ps (Maximum) Part-to-Part Skew

- 25 mV of Receiver Input Threshold Hysteresis Over 0-V to 4-V Input Voltage Range

- Inputs Electrically Compatible With LVPECL, CML, and LVDS Signal Levels

- 3.3-V Supply Operation

- LVDT Integrates 110-Ω Terminating Resistor

- Offered in SOIC and MSOP