SN65LVDS9637B

Overview

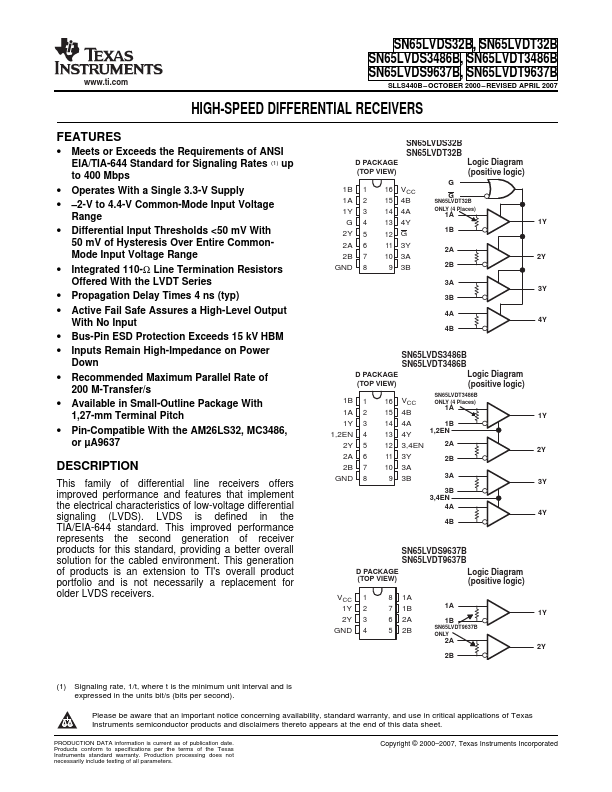

This family of differential line receivers offers improved performance and features that implement the electrical characteristics of low-voltage differential signaling (LVDS). LVDS is defined in the TIA/EIA-644 standard.

- Meets or Exceeds the Requirements of ANSI EIA/TIA-644 Standard for Signaling Rates (1) up to 400 Mbps

- Operates With a Single 3.3-V Supply

- -2-V to 4.4-V Common-Mode Input Voltage Range

- Differential Input Thresholds <50 mV With 50 mV of Hysteresis Over Entire CommonMode Input Voltage Range

- Integrated 110-Ω Line Termination Resistors Offered With the LVDT Series

- Propagation Delay Times 4 ns (typ)

- Active Fail Safe Assures a High-Level Output With No Input

- Bus-Pin ESD Protection Exceeds 15 kV HBM

- Inputs Remain High-Impedance on Power Down

- Recommended Maximum Parallel Rate of 200 M-Transfer/s