SN65MLVD2 Overview

Key Specifications

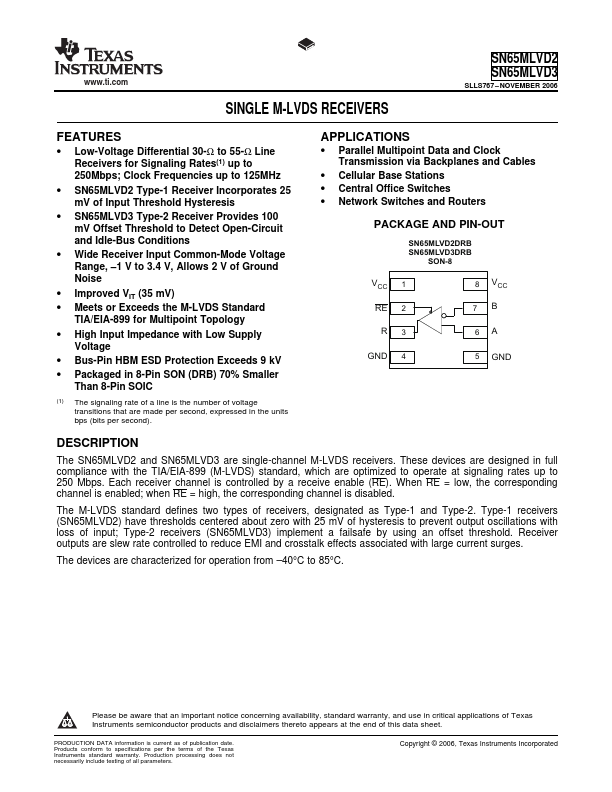

Package: SOIC

Pins: 8

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

The SN65MLVD2 and SN65MLVD3 are single-channel M-LVDS receivers. These devices are designed in full compliance with the TIA/EIA-899 (M-LVDS) standard, which are optimized to operate at signaling rates up to 250 Mbps.

Key Features

- Low-Voltage Differential 30-Ω to 55-Ω Line Receivers for Signaling Rates(1) up to 250Mbps; Clock Frequencies up to 125MHz

- SN65MLVD2 Type-1 Receiver Incorporates 25 mV of Input Threshold Hysteresis

- SN65MLVD3 Type-2 Receiver Provides 100 mV Offset Threshold to Detect Open-Circuit and Idle-Bus Conditions

- Wide Receiver Input Common-Mode Voltage Range, –1 V to 3.4 V, Allows 2 V of Ground Noise

- Improved VIT (35 mV)