| Part | SN74ABT646 |

|---|---|

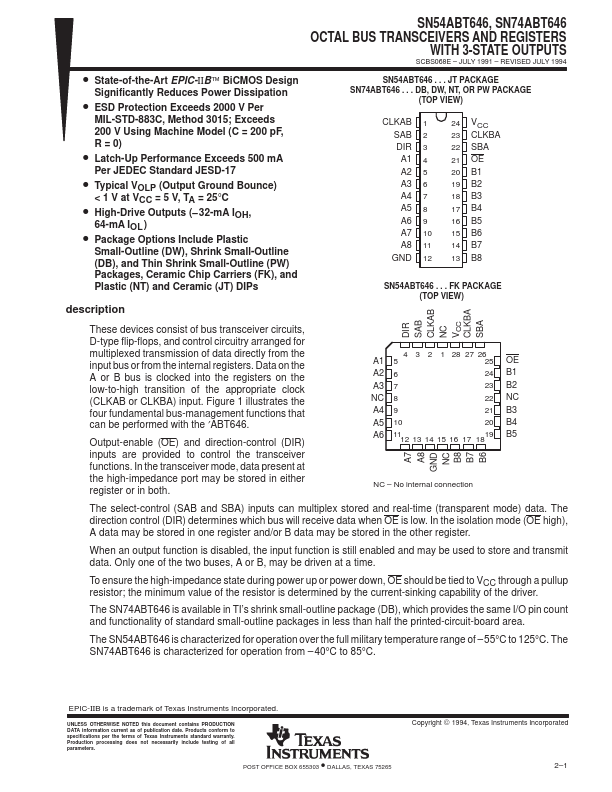

| Description | OCTAL BUS TRANSCEIVERS/REGISTERS |

| Manufacturer | Texas Instruments |

| Size | 509.25 KB |

Pricing from 1.17 USD, available from Rochester Electronics and DigiKey.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 4365 | 100+ : 1.17 USD 500+ : 1.05 USD 1000+ : 0.9711 USD 10000+ : 0.8658 USD |

View Offer |

| DigiKey | 345 | 1+ : 1.89 USD 10+ : 1.392 USD 60+ : 1.17467 USD 120+ : 1.11575 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| HC165 | Texas Instruments | 8-Bit Parallel-Load Shift Registers |

| HM74HC595 | H&M Semiconductor | 8-Bit Shift Registers |

| 74HC165 | Texas Instruments | 8-Bit Parallel-Load Shift Registers |