SN74ABTH16823 Overview

Key Specifications

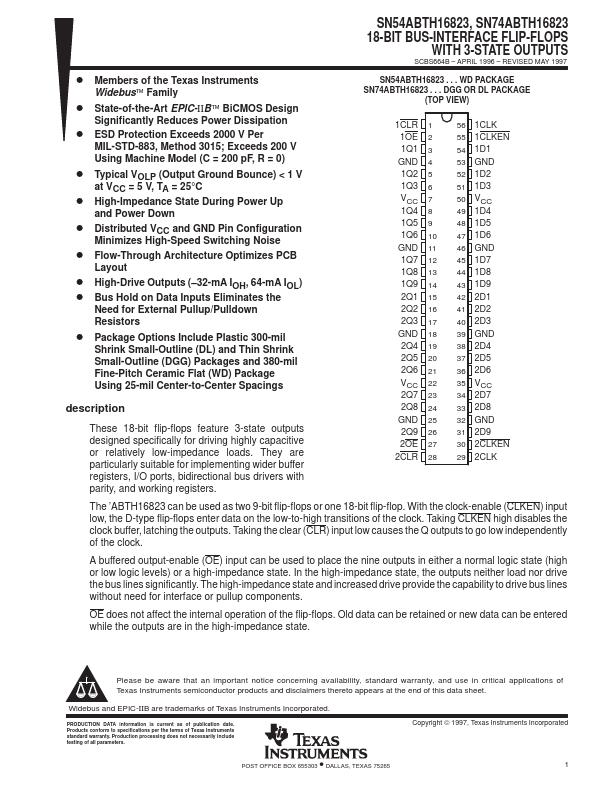

Package: SSOP

Mount Type: Surface Mount

Pins: 56

Operating Voltage: 5 V

Description

These 18-bit flip-flops feature 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing wider buffer registers, I/O ports, bidirectional bus drivers with parity, and working registers.

Key Features

- 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads

- WD PACKAGE SN74ABTH16823

- With the clock-enable (CLKEN) input low, the D-type flip-flops enter data on the low-to-high transitions of the clock

- Taking CLKEN high disables the clock buffer, latching the outputs