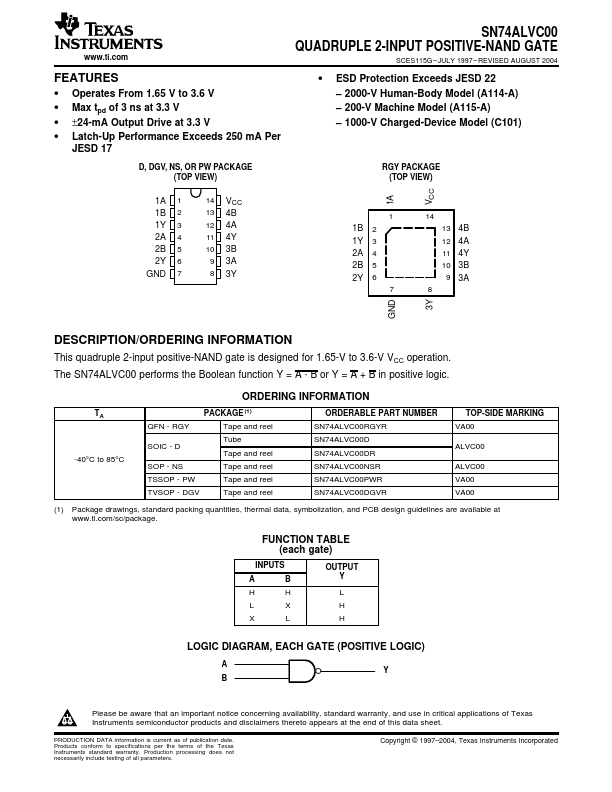

| Part | SN74ALVC00 |

|---|---|

| Description | QUADRUPLE 2-INPUT POSITIVE-NAND GATE |

| Manufacturer | Texas Instruments |

| Size | 621.91 KB |

Pricing from 0.2682 USD, available from Rochester Electronics and DigiKey.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 94000 | 100+ : 0.2682 USD 500+ : 0.2414 USD 1000+ : 0.2226 USD 10000+ : 0.1985 USD |

View Offer |

| DigiKey | 1925 | 1+ : 0.52 USD 10+ : 0.362 USD 25+ : 0.324 USD 100+ : 0.2817 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| NSi6602 | NOVOSENSE | High Reliability Isolated Dual-Channel Gate Driver |

| NSi6801 | NOVOSENSE | Single-Channel Isolated Gate Driver |

| FD2103 | Fortior | 180V Half-Bridge Gate Driver |