SN74ALVCF162834 Overview

Key Specifications

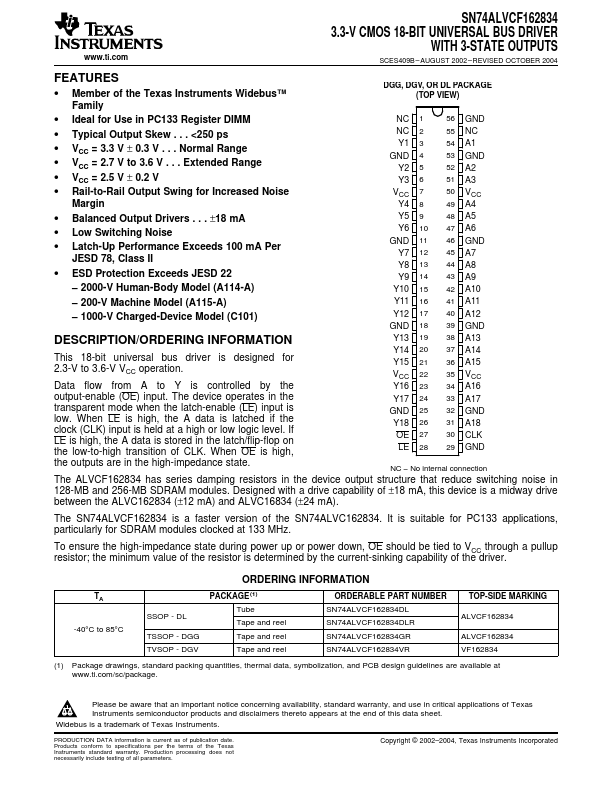

Package: SSOP

Mount Type: Surface Mount

Pins: 56

Max Voltage (typical range): 3.6 V

Key Features

- Member of the Texas Instruments Widebus™ Family DGG, DGV, OR DL PACKAGE (TOP VIEW)

- Ideal for Use in PC133 Register DIMM

- Typical Output Skew . . . <250 ps

- VCC = 3.3 V ± 0.3 V . . . Normal Range

- VCC = 2.7 V to 3.6 V . . . Extended Range