SN74AS286 Overview

Key Specifications

Package: SOIC

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 5 V

Description

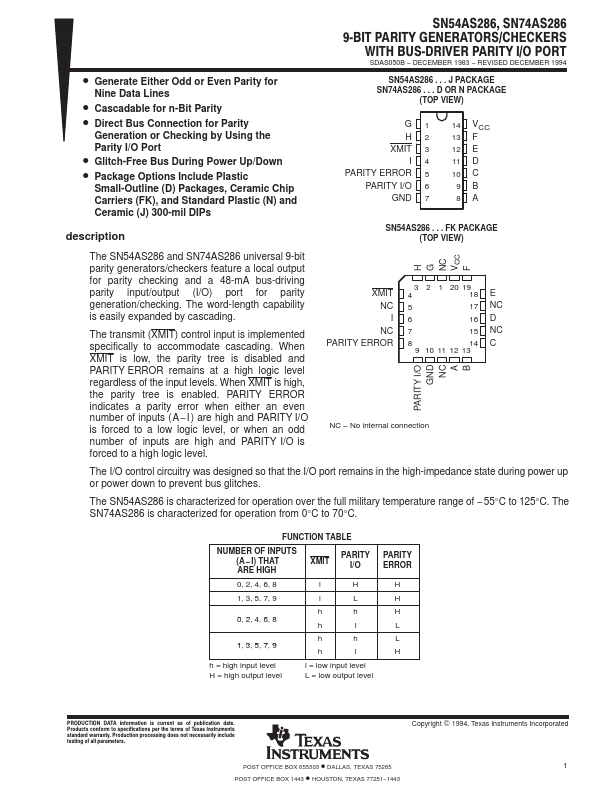

SN54AS286, SN74AS286 9ĆBIT PARITY GENERATORS/CHECKERS WITH BUSĆDRIVER PARITY I/O PORT SDAS050B - DECEMBER 1983 - REVISED DECEMBER 1994 SN54AS286. D OR N PACKAGE (TOP VIEW) G1 H2 XMIT 3 I4 PARITY ERROR 5 PARITY I/O 6 GND 7 14 VCC 13 F 12 E 11 D 10 C 9B 8A SN54AS286.

Key Features

- a local output for parity checking and a 48-mA bus-driving parity input/output (I/O) port for parity generation/checking

- The word-length capability is easily expanded by cascading

- The transmit (XMIT) control input is implemented specifically to accommodate cascading

- When XMIT is low, the parity tree is disabled and PARITY ERROR remains at a high logic level regardless of the input levels

- When XMIT is high, the parity tree is enabled