SN74AS825A Overview

Key Specifications

Package: DIP

Mount Type: Through Hole

Pins: 24

Operating Voltage: 5 V

Description

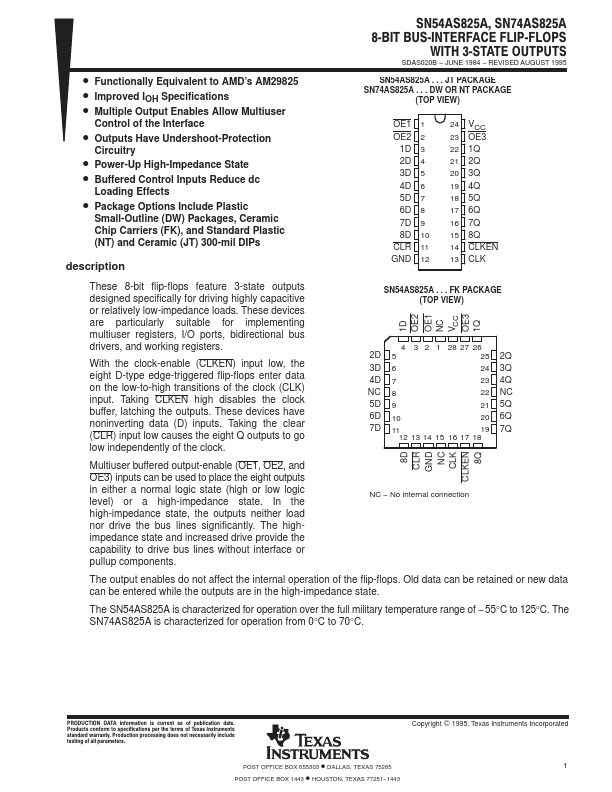

SN54AS825A, SN74AS825A 8ĆBIT BUSĆINTERFACE FLIPĆFLOPS WITH 3ĆSTATE OUTPUTS SDAS020B - JUNE 1984 - REVISED AUGUST 1995 SN54AS825A. JT PACKAGE SN74AS825A.

Key Features

- 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads

- These devices are particularly suitable for implementing multiuser registers, I/O ports, bidirectional bus drivers, and working registers

- Taking CLKEN high disables the clock buffer, latching the outputs

- These devices have noninverting data (D) inputs

- Taking the clear (CLR) input low causes the eight Q outputs to go low independently of the clock