SN74AS867 Overview

Key Specifications

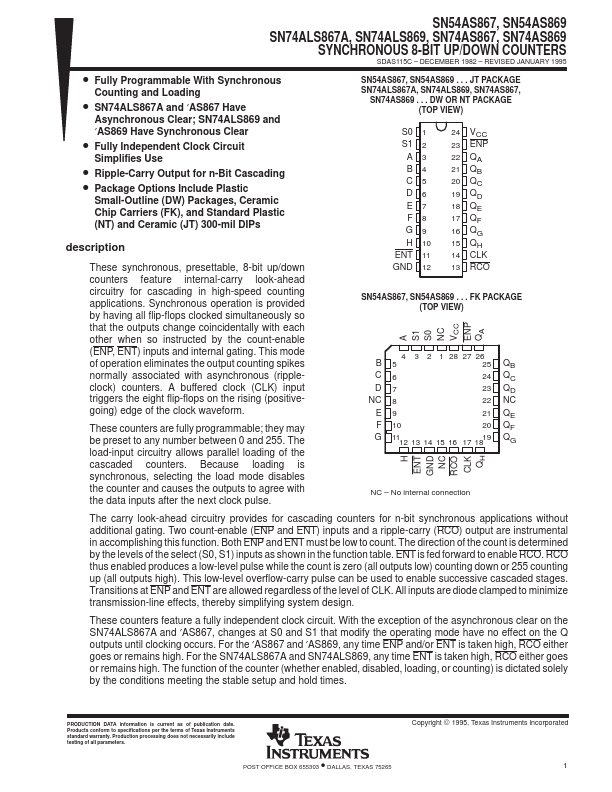

Package: PDIP

Mount Type: Through Hole

Pins: 24

Operating Voltage: 5 V

Description

These synchronous, presettable, 8-bit up/down counters feature internal-carry look-ahead circuitry for cascading in high-speed counting applications. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincidentally with each other when so instructed by the count-enable (ENP, ENT) inputs and internal gating.

Key Features

- internal-carry look-ahead circuitry for cascading in high-speed counting applications

- This mode of operation eliminates the output counting spikes normally associated with asynchronous (rippleclock) counters

- A buffered clock (CLK) input triggers the eight flip-flops on the rising (positivegoing) edge of the clock waveform

- SN54AS867, SN54AS869