SN74AUP1T08 Overview

Key Specifications

Package: SC

Mount Type: Surface Mount

Pins: 5

Max Voltage (typical range): 3.6 V

Description

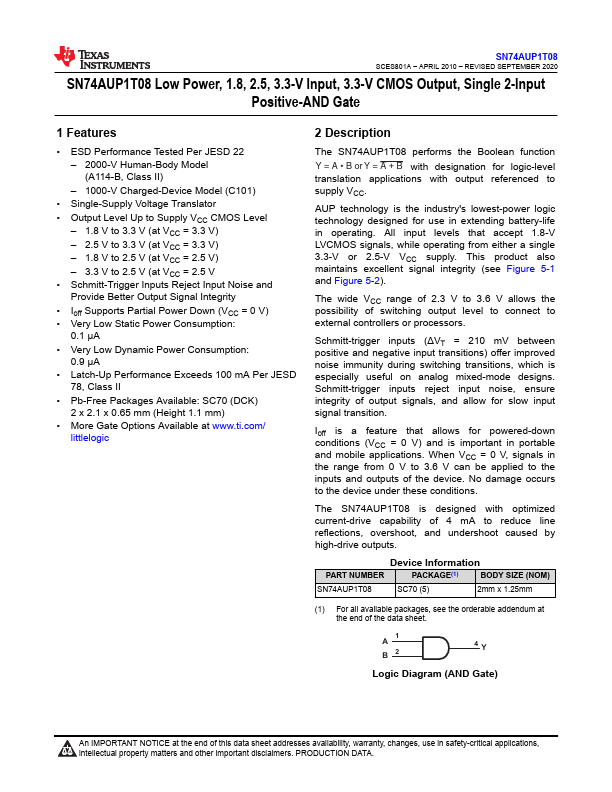

The SN74AUP1T08 performs the Boolean function Y = A - B or Y = A + B with designation for logic-level translation applications with output referenced to supply VCC. AUP technology is the industry's lowest-power logic technology designed for use in extending battery-life in operating.

Key Features

- ESD Performance Tested Per JESD 22 – 2000-V Human-Body Model (A114-B, Class II) – 1000-V Charged-Device Model (C101)

- Single-Supply Voltage Translator

- Schmitt-Trigger Inputs Reject Input Noise and Provide Better Output Signal Integrity

- Ioff Supports Partial Power Down (VCC = 0 V)

- Very Low Static Power Consumption: 0.1 µA