SN74LV4046A Overview

Key Specifications

Package: SOIC

Mount Type: Surface Mount

Pins: 16

Max Voltage (typical range): 5.5 V

Description

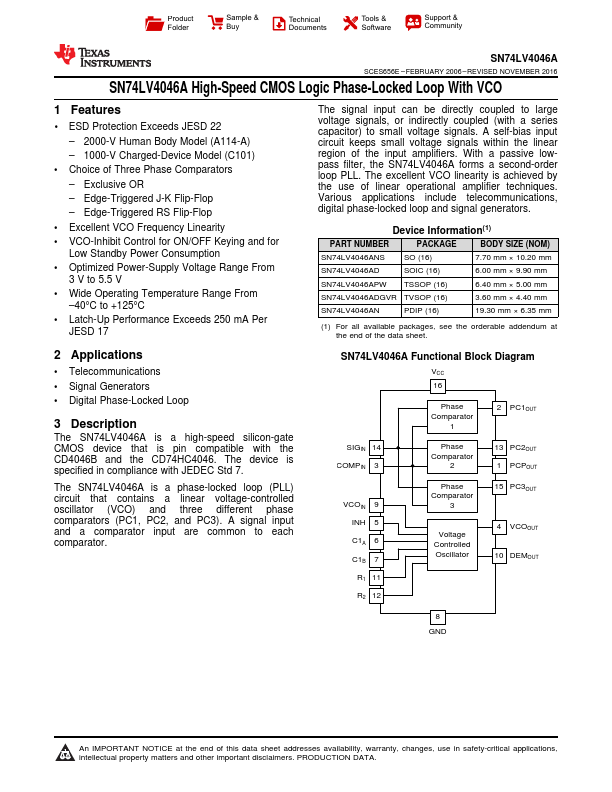

The SN74LV4046A is a high-speed silicon-gate CMOS device that is pin compatible with the CD4046B and the CD74HC4046. The device is specified in compliance with JEDEC Std 7.

Key Features

- 1 ESD Protection Exceeds JESD 22 – 2000-V Human Body Model (A114-A) – 1000-V Charged-Device Model (C101)

- Choice of Three Phase Comparators – Exclusive OR – Edge-Triggered J-K Flip-Flop – Edge-Triggered RS Flip-Flop

- Excellent VCO Frequency Linearity

- VCO-Inhibit Control for ON/OFF Keying and for Low Standby Power Consumption

- Optimized Power-Supply Voltage Range From 3 V to 5.5 V