SN74LVC2952A

SN74LVC2952A is OCTAL BUS TRANSCEIVER AND REGISTER manufactured by Texas Instruments.

FEATURES

- Operates From 1.65 V to 3.6 V

- Inputs Accept Voltages to 5.5 V

- Max tpd of 8.2 ns at 3.3 V

- Typical VOLP (Output Ground Bounce)

<0.8 V at VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot)

>2 V at VCC = 3.3 V, TA = 25°C

- Supports Mixed-Mode Signal Operation on All

Ports (5-V Input/Output Voltage With 3.3-V VCC)

- Ioff Supports Partial-Power-Down Mode Operation

- Latch-Up Performance Exceeds 250 m A Per JESD 17

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 1000-V Charged-Device Model (C101)

SN74LVC2952A OCTAL BUS TRANSCEIVER AND REGISTER

WITH 3-STATE OUTPUTS

SCAS311I

- JANUARY 1993

- REVISED MARCH 2005

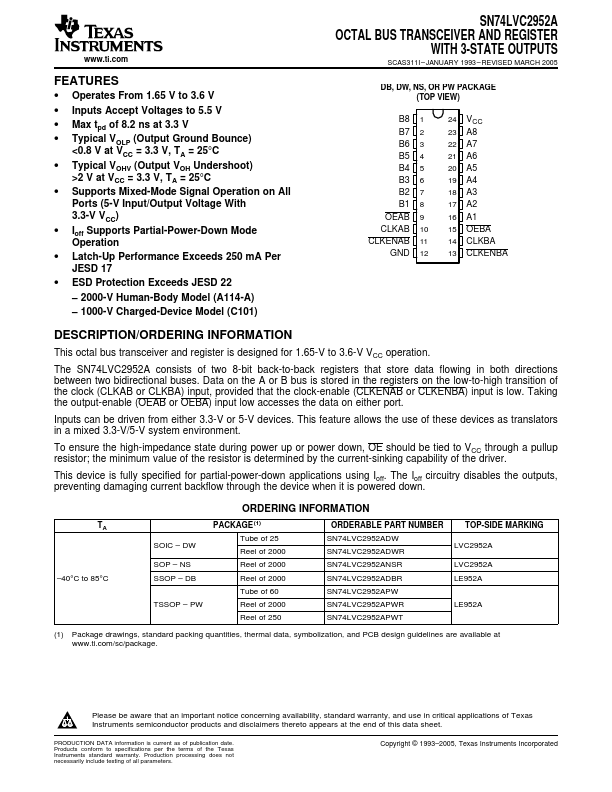

DB, DW, NS, OR PW PACKAGE (TOP VIEW)

B8 1 B7 2 B6 3 B5 4 B4 5 B3 6 B2 7 B1 8 OEAB 9 CLKAB 10 CLKENAB 11 GND 12

24 VCC 23 A8 22 A7 21 A6 20 A5 19 A4 18 A3 17 A2 16 A1 15 OEBA 14 CLKBA 13 CLKENBA

DESCRIPTION

/ORDERING INFORMATION

This octal bus transceiver and register is designed for 1.65-V to 3.6-V VCC operation.

The SN74LVC2952A consists of two 8-bit back-to-back registers that store data flowing in both directions between two bidirectional buses. Data on the A or B bus is stored in the registers on the low-to-high transition of the clock (CLKAB or CLKBA) input, provided that the clock-enable (CLKENAB or CLKENBA) input is low. Taking the output-enable (OEAB or OEBA) input low accesses the data on either port.

Inputs can be driven from either 3.3-V or 5-V devices. This feature allows the use of these devices as translators in a mixed 3.3-V/5-V system environment.

To ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

This device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

- 40°C to 85°C

SOIC

- DW SOP

- NS SSOP

-...