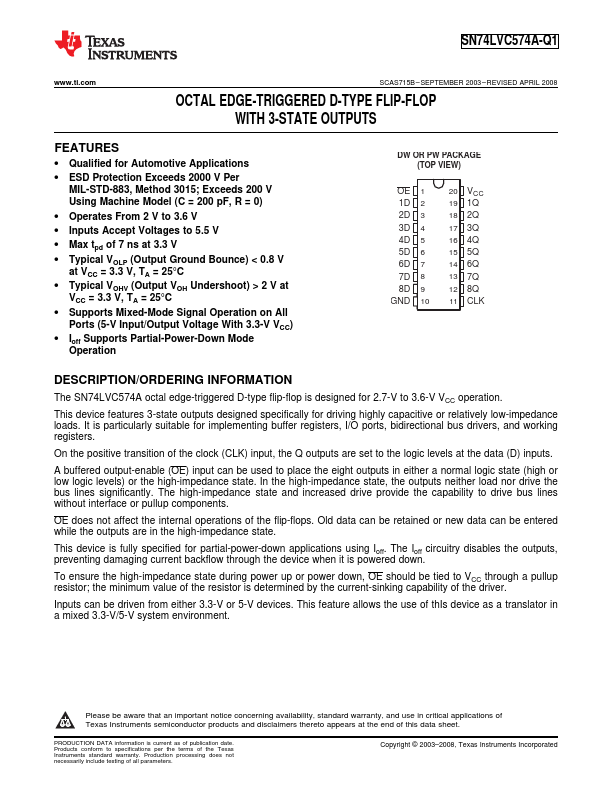

SN74LVC574A-Q1 Overview

Key Specifications

Output Type (varies by manufacturer): CMOS

Key Features

- Qualified for Automotive Applications

- ESD Protection Exceeds 2000 V Per MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R =

- Operates From 2 V to 3.6 V

- Inputs Accept Voltages to 5.5 V

- Max tpd of 7 ns at 3.3 V