SN74LVT574 Overview

Key Specifications

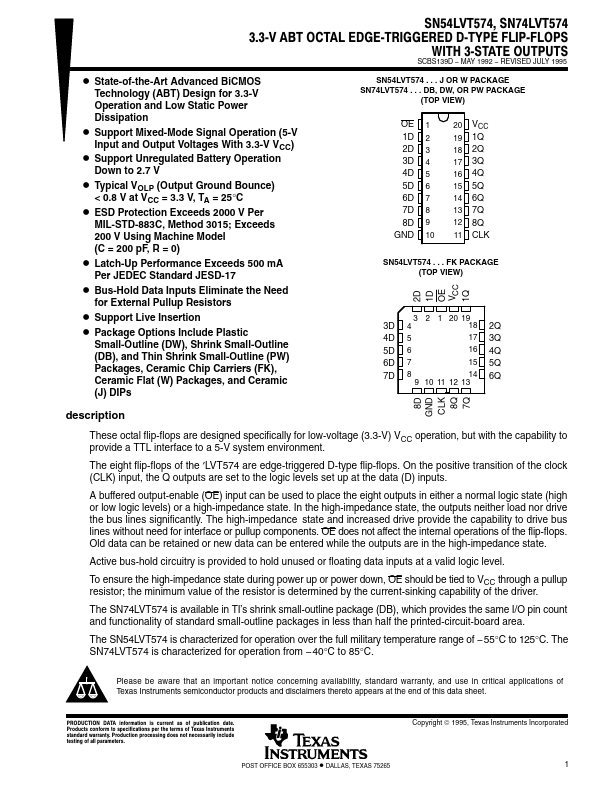

Package: TSSOP

Mount Type: Surface Mount

Pins: 20

Operating Voltage: 3.3 V

Description

These octal flip-flops are designed specifically for low-voltage (3.3-V) VCC operation, but with the capability to provide a TTL interface to a 5-V system environment. The eight flip-flops of the ′LVT574 are edge-triggered D-type flip-flops.