SN74LVTH16374 Overview

Key Specifications

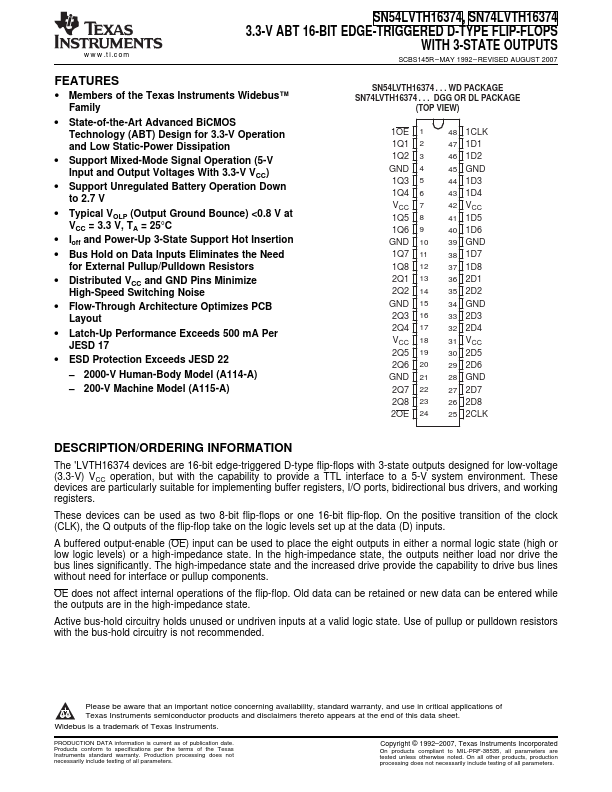

Package: SSOP

Mount Type: Surface Mount

Pins: 48

Operating Voltage: 3.3 V

Key Features

- 2 Members of the Texas Instruments Widebus™ Family

- State-of-the-Art Advanced BiCMOS Technology (ABT) Design for 3.3-V Operation and Low Static-Power Dissipation

- Support Mixed-Mode Signal Operation (5-V Input and Output Voltages With 3.3-V VCC)

- Support Unregulated Battery Operation Down to 2.7 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25°C