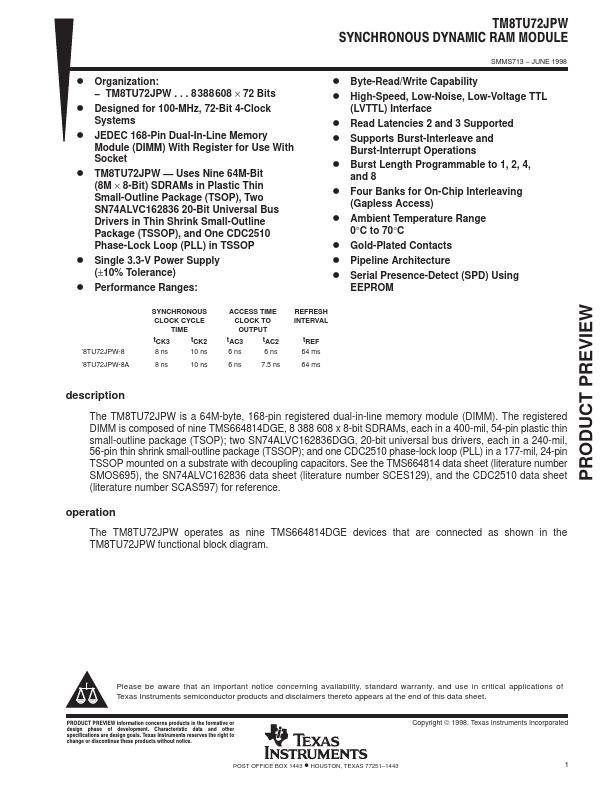

TM8TU72JPW Description

The TM8TU72JPW is a 64M-byte, 168-pin registered dual-in-line memory module (DIMM). The registered DIMM is posed of nine TMS664814DGE, 8 388 608 x 8-bit SDRAMs, each in a 400-mil, 54-pin plastic thin small-outline package (TSOP); two SN74ALVC162836DGG, 20-bit universal bus drivers, each in a 240-mil, 56-pin thin shrink small-outline package (TSSOP);.