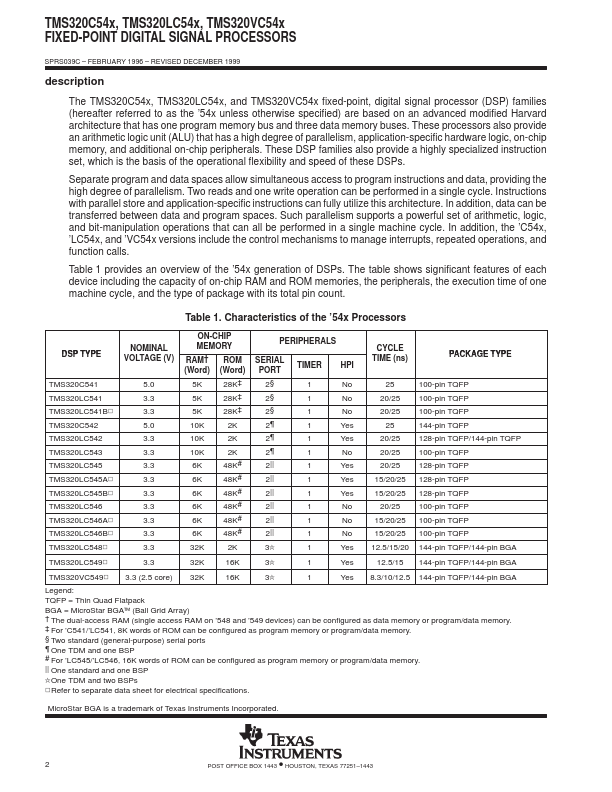

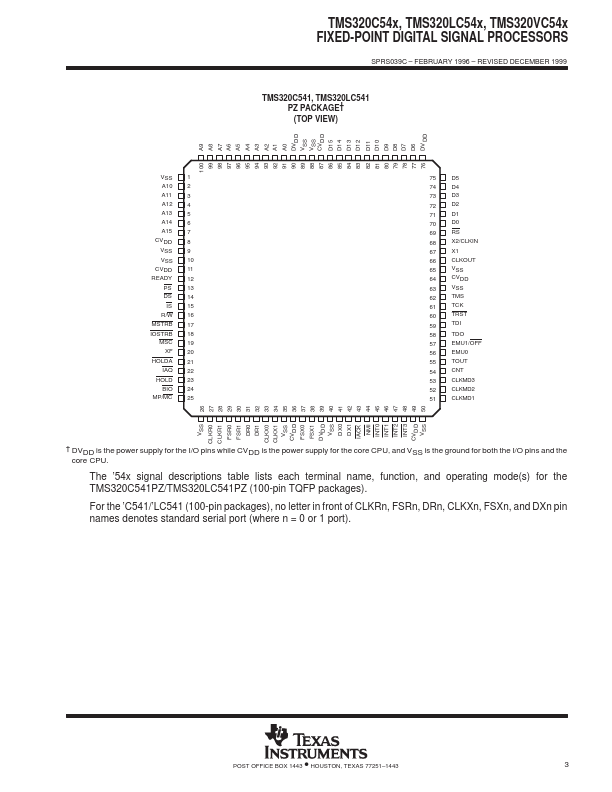

TMS320C541 Overview

TMS320C54x, TMS320LC54x, TMS320VC54x FIXED-POINT DIGITAL SIGNAL PROCESSORS D Advanced Multibus Architecture With Three Separate 16-Bit Data Memory Buses and One Program Memory Bus D 40-Bit Arithmetic Logic Unit (ALU) Including a 40-Bit Barrel Shifter and Two.