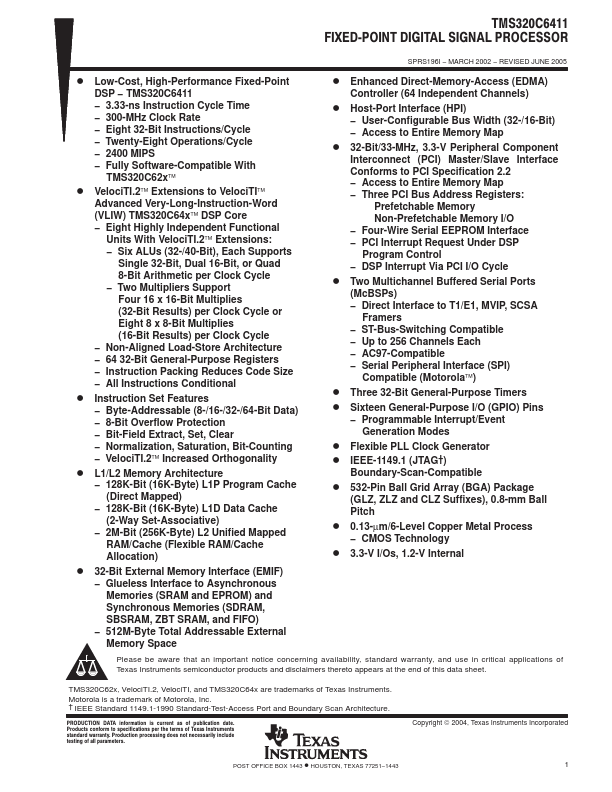

TMS320C6411

Overview

- L1/L2 Memory Architecture - 128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped) - 128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative) - 2M-Bit (256K-Byte) L2 Unified Mapped RAM/Cache (Flexible RAM/Cache Allocation)

- 32-Bit External Memory Interface (EMIF) - Glueless Interface to Asynchronous Memories (SRAM and EPROM) and Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM, and FIFO) - 512M-Byte Total Addressable External Memory Space

- Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels)

- Host-Port Interface (HPI) - User-Configurable Bus Width (32-/16-Bit) - Access to Entire Memory Map

- 32-Bit/33-MHz, 3.3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Specification 2.2 - Access to Entire Memory Map - Three PCI Bus Address Registers: