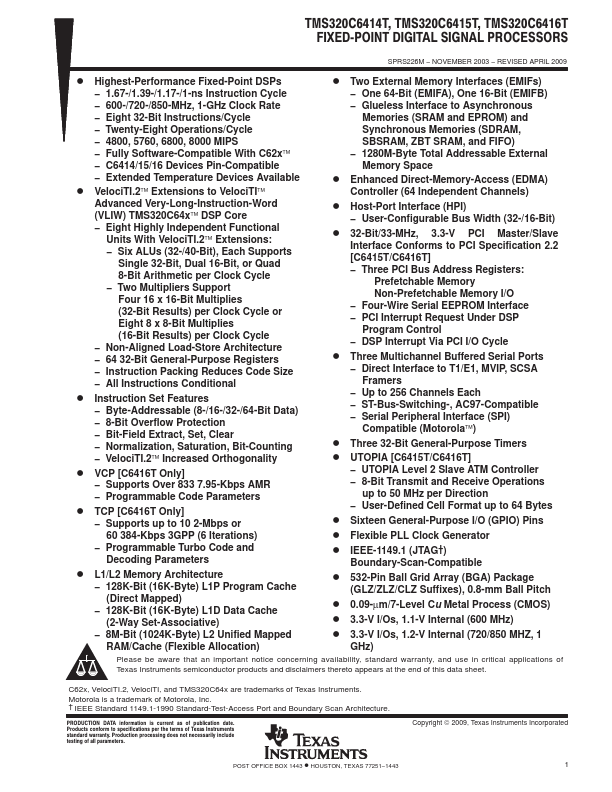

TMS320C6415T Overview

Key Specifications

Package: FCBGA

Mount Type: Surface Mount

Pins: 532

Operating Voltage: 1.2 V

Key Features

- 8-Bit Overflow Protection

- Normalization, Saturation, Bit-Counting

- VelociTI.2 Increased Orthogonality D Host-Port Interface (HPI)

- User-Configurable Bus Width (32-/16-Bit) D 32-Bit/33-MHz, 3.3-V PCI Master/Slave Interface Conforms to PCI Specification 2.2 [C6415T/C6416T]

- Three PCI Bus Address Registers: Prefetchable Memory Non-Prefetchable Memory I/O